CY7C1440AV33

CY7C1442AV33

CY7C1446AV33

The shifting of data for the SAMPLE and PRELOAD phases can occur concurrently when

BYPASS

When the BYPASS instruction is loaded in the instruction register and the TAP is placed in a

EXTEST

The EXTEST instruction enables the preloaded data to be driven out through the system output pins. This instruction also selects the boundary scan register to be connected for serial access between the TDI and TDO in the

EXTEST OUTPUT BUS TRI-STATE

IEEE Standard 1149.1 mandates that the TAP controller be able to put the output bus into a

The boundary scan register has a special bit located at, bit #89 (for

This bit can be set by entering the SAMPLE/PRELOAD or EXTEST command, and then shifting the desired bit into that cell, during the

Reserved

These instructions are not implemented but are reserved for future use. Do not use these instructions.

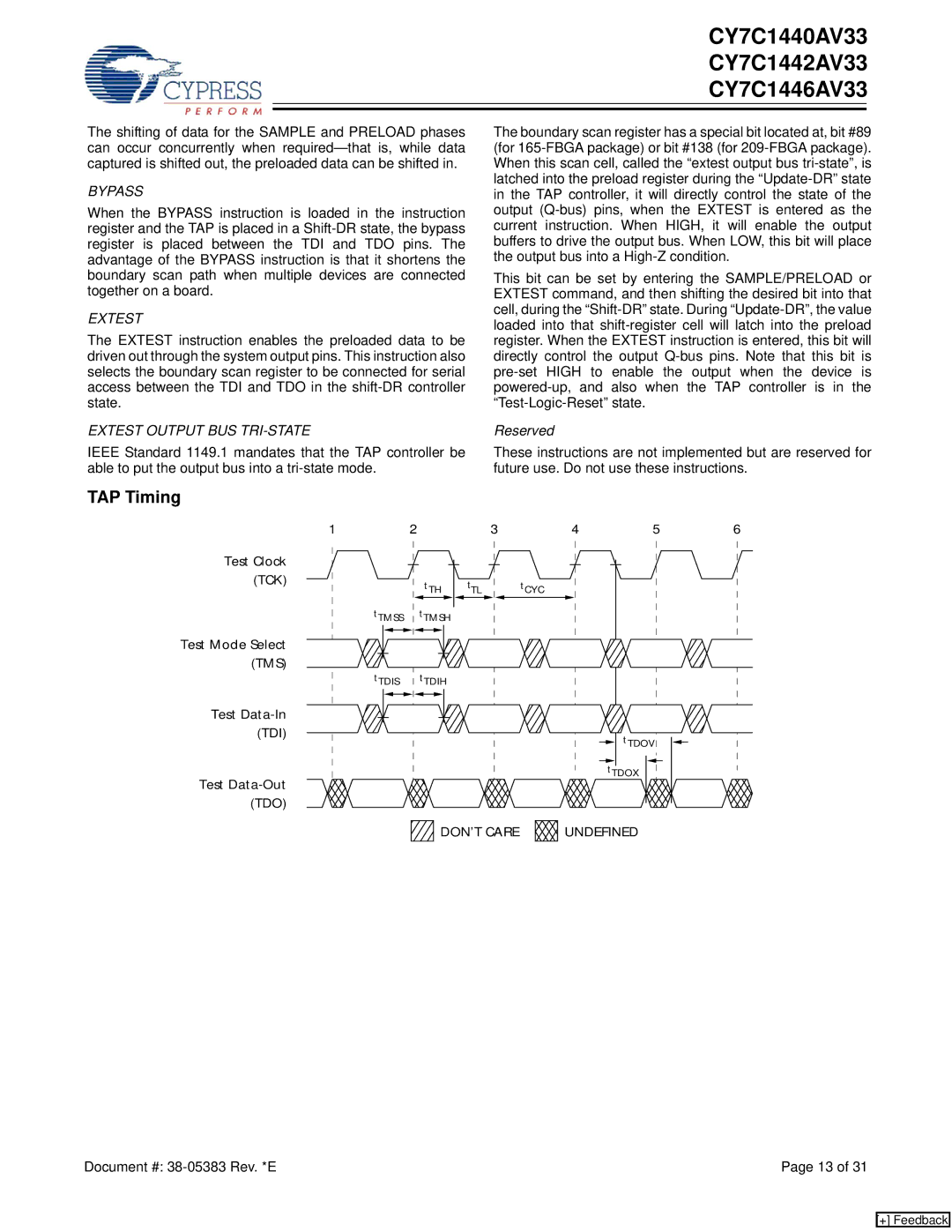

TAP Timing

12

Test Clock

(TCK)tTH

tTMSS tTMSH

Test Mode Select (TMS)

tTDIS tTDIH

Test

3 | 4 | 5 | 6 |

tTL tCYC

tTDOV

tTDOX

Test

DON’T CARE | UNDEFINED |

Document #: | Page 13 of 31 |

[+] Feedback