|

|

|

|

|

|

|

|

|

|

|

|

| CY7C1440AV33 | |

|

|

|

|

|

|

|

|

|

|

|

|

| CY7C1442AV33 | |

|

|

|

|

|

|

|

|

|

|

|

|

| CY7C1446AV33 | |

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

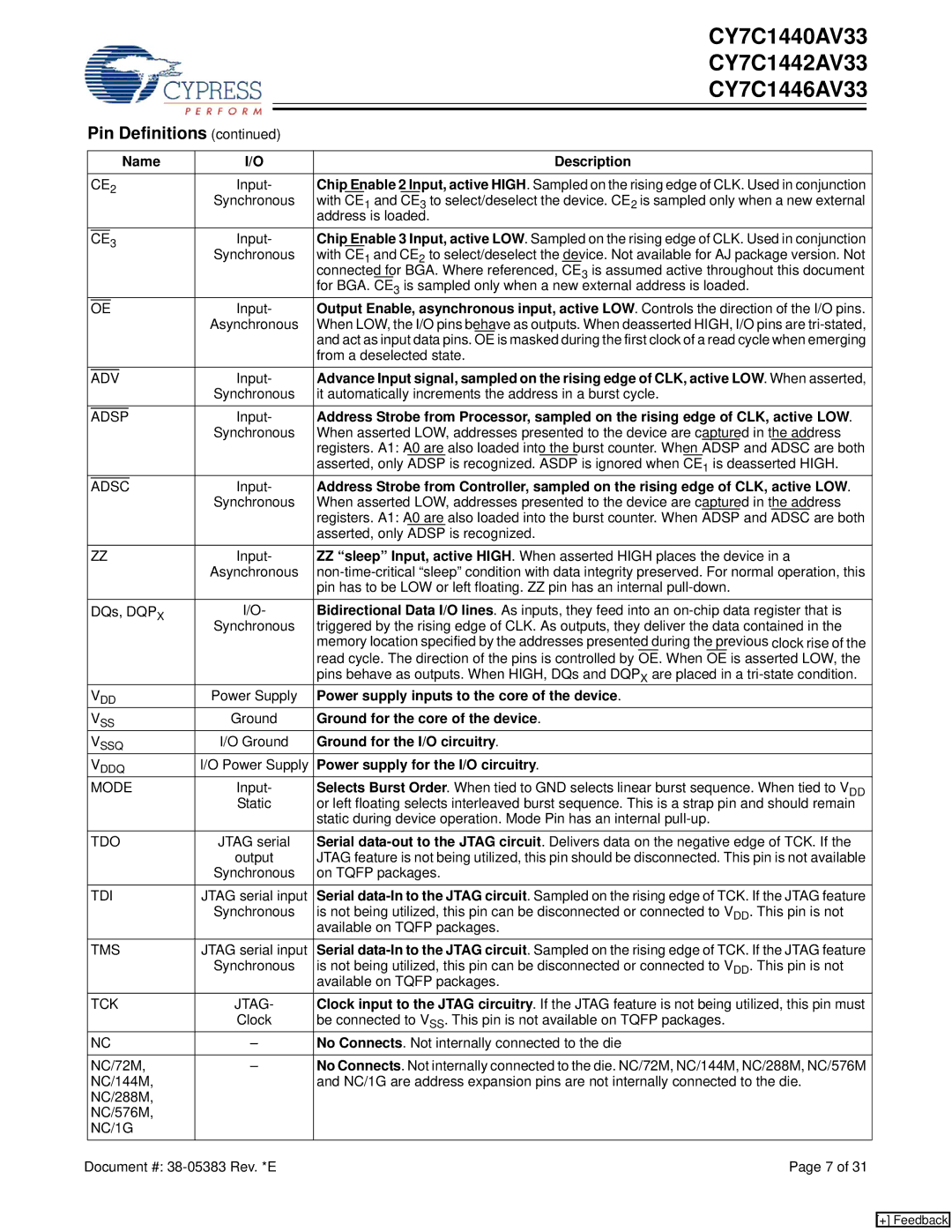

| Pin Definitions (continued) |

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| Name | I/O |

|

| Description | |||||

|

|

|

|

| ||||||||||

|

| CE2 | Input- | Chip Enable 2 Input, active HIGH. Sampled on the rising edge of CLK. Used in conjunction | ||||||||||

|

|

| ||||||||||||

|

|

|

|

|

|

|

| Synchronous | with CE1 and CE3 to select/deselect the device. CE2 is sampled only when a new external | |||||

|

|

|

|

|

|

|

|

|

|

| address is loaded. | |||

|

|

| 3 |

|

|

| Input- | Chip Enable 3 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction | ||||||

|

| CE | ||||||||||||

|

|

|

|

|

|

|

| Synchronous | with CE1 and CE2 to select/deselect the device. Not available for AJ package version. Not | |||||

|

|

|

|

|

|

|

|

|

|

| connected for BGA. Where referenced, CE3 is assumed active throughout this document | |||

|

|

|

|

|

|

|

|

|

|

| for BGA. CE3 is sampled only when a new external address is loaded. | |||

|

|

|

|

|

|

|

| Input- | Output Enable, asynchronous input, active LOW. Controls the direction of the I/O pins. | |||||

|

| OE | ||||||||||||

|

|

|

|

|

|

|

| Asynchronous | When LOW, the I/O pins behave as outputs. When deasserted HIGH, I/O pins are | |||||

|

|

|

|

|

|

|

|

|

|

| and act as input data pins. OE is masked during the first clock of a read cycle when emerging | |||

|

|

|

|

|

|

|

|

|

|

| from a deselected state. | |||

|

|

|

|

|

|

|

| Input- | Advance Input signal, sampled on the rising edge of CLK, active LOW. When asserted, | |||||

|

| ADV | ||||||||||||

|

|

|

|

|

|

|

| Synchronous | it automatically increments the address in a burst cycle. | |||||

|

|

|

|

|

|

|

| Input- | Address Strobe from Processor, sampled on the rising edge of CLK, active LOW. | |||||

|

| ADSP | ||||||||||||

|

|

|

|

|

|

|

| Synchronous | When asserted LOW, addresses presented to the device are captured in the address | |||||

|

|

|

|

|

|

|

|

|

|

| registers. A1: A0 are also loaded into the burst counter. When ADSP and ADSC are both | |||

|

|

|

|

|

|

|

|

|

|

| asserted, only ADSP is recognized. ASDP is ignored when CE1 is deasserted HIGH. | |||

|

|

|

|

|

|

|

| Input- | Address Strobe from Controller, sampled on the rising edge of CLK, active LOW. | |||||

|

| ADSC | ||||||||||||

|

|

|

|

|

|

|

| Synchronous | When asserted LOW, addresses presented to the device are captured in the address | |||||

|

|

|

|

|

|

|

|

|

|

| registers. A1: A0 are also loaded into the burst counter. When ADSP and ADSC are both | |||

|

|

|

|

|

|

|

|

|

|

| asserted, only ADSP is recognized. | |||

|

| ZZ | Input- | ZZ “sleep” Input, active HIGH. When asserted HIGH places the device in a | ||||||||||

|

|

|

|

|

|

|

| Asynchronous | ||||||

|

|

|

|

|

|

|

|

|

|

| pin has to be LOW or left floating. ZZ pin has an internal | |||

|

| DQs, DQPX | I/O- | Bidirectional Data I/O lines. As inputs, they feed into an | ||||||||||

|

|

|

|

|

|

|

| Synchronous | triggered by the rising edge of CLK. As outputs, they deliver the data contained in the | |||||

|

|

|

|

|

|

|

|

|

|

| memory location specified by the addresses presented during the previous clock rise of the | |||

|

|

|

|

|

|

|

|

|

|

| read cycle. The direction of the pins is controlled by OE. When OE is asserted LOW, the | |||

|

|

|

|

|

|

|

|

|

|

| pins behave as outputs. When HIGH, DQs and DQPX are placed in a | |||

|

| VDD | Power Supply | Power supply inputs to the core of the device. | ||||||||||

|

| VSS | Ground | Ground for the core of the device. | ||||||||||

|

| VSSQ | I/O Ground | Ground for the I/O circuitry. | ||||||||||

|

| VDDQ | I/O Power Supply | Power supply for the I/O circuitry. | ||||||||||

|

| MODE | Input- | Selects Burst Order. When tied to GND selects linear burst sequence. When tied to VDD | ||||||||||

|

|

|

|

|

|

|

| Static | or left floating selects interleaved burst sequence. This is a strap pin and should remain | |||||

|

|

|

|

|

|

|

|

|

|

| static during device operation. Mode Pin has an internal | |||

|

| TDO | JTAG serial | Serial | ||||||||||

|

|

|

|

|

|

|

| output | JTAG feature is not being utilized, this pin should be disconnected. This pin is not available | |||||

|

|

|

|

|

|

|

| Synchronous | on TQFP packages. | |||||

|

| TDI | JTAG serial input | Serial | ||||||||||

|

|

|

|

|

|

|

| Synchronous | is not being utilized, this pin can be disconnected or connected to VDD. This pin is not | |||||

|

|

|

|

|

|

|

|

|

|

| available on TQFP packages. | |||

|

| TMS | JTAG serial input | Serial | ||||||||||

|

|

|

|

|

|

|

| Synchronous | is not being utilized, this pin can be disconnected or connected to VDD. This pin is not | |||||

|

|

|

|

|

|

|

|

|

|

| available on TQFP packages. | |||

|

| TCK | JTAG- | Clock input to the JTAG circuitry. If the JTAG feature is not being utilized, this pin must | ||||||||||

|

|

|

|

|

|

|

| Clock | be connected to VSS. This pin is not available on TQFP packages. | |||||

|

| NC | – | No Connects. Not internally connected to the die | ||||||||||

|

|

|

|

| ||||||||||

|

| NC/72M, | – | No Connects. Not internally connected to the die. NC/72M, NC/144M, NC/288M, NC/576M | ||||||||||

|

| NC/144M, |

|

|

| and NC/1G are address expansion pins are not internally connected to the die. | ||||||||

|

| NC/288M, |

|

|

|

|

|

|

| |||||

|

| NC/576M, |

|

|

|

|

|

|

| |||||

|

| NC/1G |

|

|

|

|

|

|

| |||||

Document #: |

|

| Page 7 of 31 | |||||||||||

[+] Feedback