CYDC256B16, CYDC128B16,

CYDC064B16, CYDC128B08,

CYDC064B08

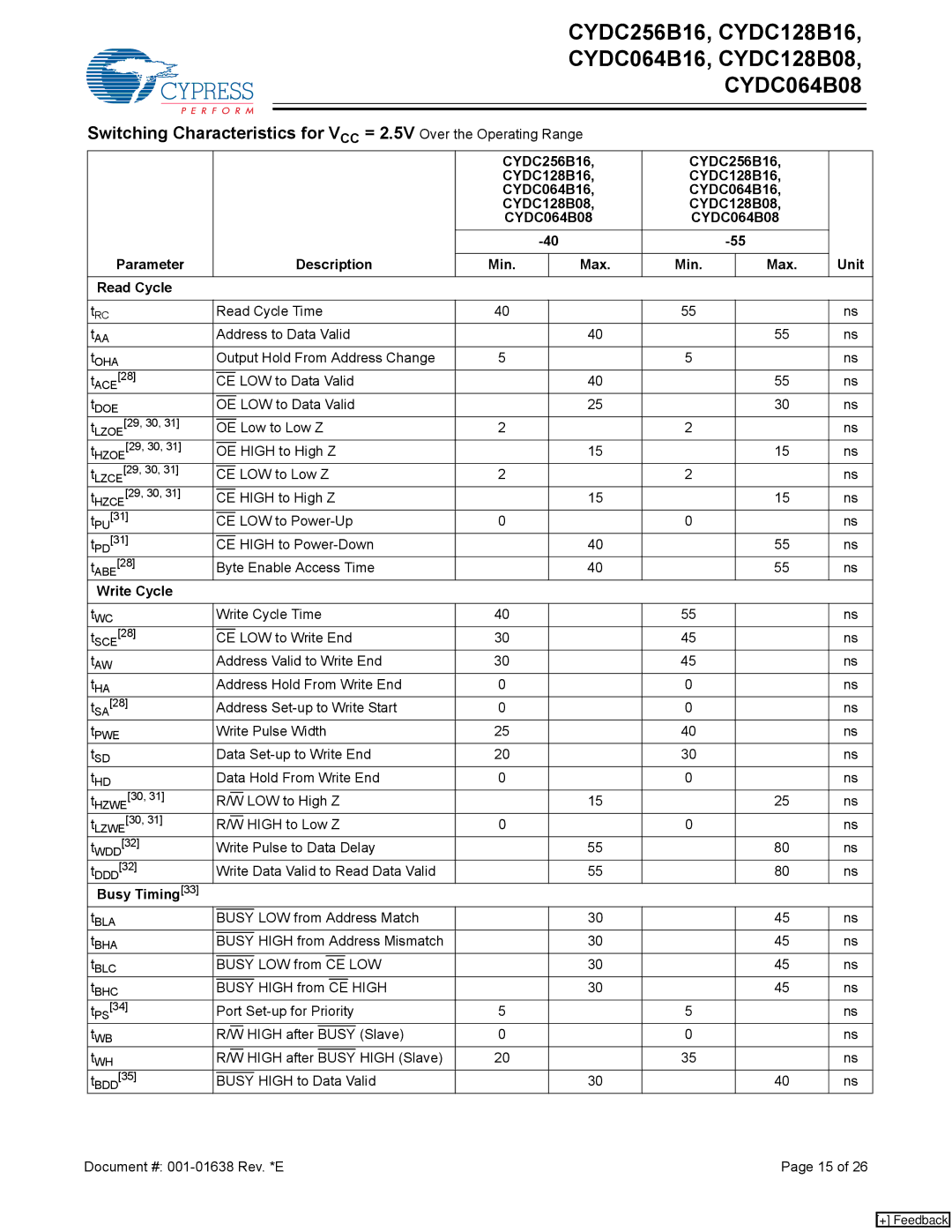

Switching Characteristics for VCC = 2.5V Over the Operating Range

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CYDC256B16, | CYDC256B16, |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CYDC128B16, | CYDC128B16, |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CYDC064B16, | CYDC064B16, |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CYDC128B08, | CYDC128B08, |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CYDC064B08 | CYDC064B08 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

Parameter |

|

|

|

|

|

|

|

| Description |

|

|

|

|

|

| Unit | ||||||

|

|

|

|

|

|

|

| Min. |

| Max. | Min. |

| Max. | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read Cycle |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| ||||||||||||||

tRC |

| Read Cycle Time | 40 |

|

| 55 |

|

| ns | |||||||||||||

tAA |

| Address to Data Valid |

|

| 40 |

|

| 55 | ns | |||||||||||||

tOHA |

| Output Hold From Address Change | 5 |

|

| 5 |

|

| ns | |||||||||||||

tACE[28] |

|

|

|

| LOW to Data Valid |

|

| 40 |

|

| 55 | ns | ||||||||||

CE |

|

| ||||||||||||||||||||

tDOE |

|

|

|

| LOW to Data Valid |

|

| 25 |

|

| 30 | ns | ||||||||||

OE |

|

| ||||||||||||||||||||

tLZOE[29, 30, 31] |

|

|

|

| Low to Low Z | 2 |

|

| 2 |

|

| ns | ||||||||||

OE |

|

|

|

| ||||||||||||||||||

tHZOE[29, 30, 31] |

|

|

|

| HIGH to High Z |

|

| 15 |

|

| 15 | ns | ||||||||||

OE |

|

| ||||||||||||||||||||

tLZCE[29, 30, 31] |

|

|

| LOW to Low Z | 2 |

|

| 2 |

|

| ns | |||||||||||

CE |

|

|

|

| ||||||||||||||||||

tHZCE[29, 30, 31] |

|

|

| HIGH to High Z |

|

| 15 |

|

| 15 | ns | |||||||||||

CE |

|

| ||||||||||||||||||||

tPU[31] |

|

|

| LOW to | 0 |

|

| 0 |

|

| ns | |||||||||||

CE |

|

|

|

| ||||||||||||||||||

tPD[31] |

|

|

| HIGH to |

|

| 40 |

|

| 55 | ns | |||||||||||

CE |

|

| ||||||||||||||||||||

tABE[28] |

| Byte Enable Access Time |

|

| 40 |

|

| 55 | ns | |||||||||||||

Write Cycle |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| ||||||||||||||

tWC |

| Write Cycle Time | 40 |

|

| 55 |

|

| ns | |||||||||||||

tSCE[28] |

|

|

| LOW to Write End | 30 |

|

| 45 |

|

| ns | |||||||||||

CE |

|

|

|

| ||||||||||||||||||

tAW |

| Address Valid to Write End | 30 |

|

| 45 |

|

| ns | |||||||||||||

tHA |

| Address Hold From Write End | 0 |

|

| 0 |

|

| ns | |||||||||||||

tSA[28] |

| Address | 0 |

|

| 0 |

|

| ns | |||||||||||||

tPWE |

| Write Pulse Width | 25 |

|

| 40 |

|

| ns | |||||||||||||

tSD |

| Data | 20 |

|

| 30 |

|

| ns | |||||||||||||

tHD |

| Data Hold From Write End | 0 |

|

| 0 |

|

| ns | |||||||||||||

tHZWE[30, 31] |

|

|

|

|

|

| LOW to High Z |

|

| 15 |

|

| 25 | ns | ||||||||

R/W |

|

| ||||||||||||||||||||

tLZWE[30, 31] |

|

|

|

|

|

| HIGH to Low Z | 0 |

|

| 0 |

|

| ns | ||||||||

R/W |

|

|

|

| ||||||||||||||||||

tWDD[32] |

| Write Pulse to Data Delay |

|

| 55 |

|

| 80 | ns | |||||||||||||

tDDD[32] |

| Write Data Valid to Read Data Valid |

|

| 55 |

|

| 80 | ns | |||||||||||||

Busy Timing[33] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tBLA |

| BUSY |

| LOW from Address Match |

|

| 30 |

|

| 45 | ns | |||||||||||

tBHA |

|

|

|

|

|

|

|

| HIGH from Address Mismatch |

|

| 30 |

|

| 45 | ns | ||||||

BUSY |

|

| ||||||||||||||||||||

tBLC |

|

|

|

|

|

|

|

| LOW from |

|

|

| LOW |

|

| 30 |

|

| 45 | ns | ||

BUSY | CE |

|

| |||||||||||||||||||

tBHC |

|

|

|

|

|

|

|

| HIGH from |

|

| HIGH |

|

| 30 |

|

| 45 | ns | |||

BUSY | CE |

|

| |||||||||||||||||||

tPS[34] |

| Port | 5 |

|

| 5 |

|

| ns | |||||||||||||

tWB |

|

|

|

|

| HIGH after |

|

|

|

|

| (Slave) | 0 |

|

| 0 |

|

| ns | |||

R/W | BUSY |

|

|

|

| |||||||||||||||||

tWH |

|

|

|

|

|

| HIGH after |

|

|

|

|

| HIGH (Slave) | 20 |

|

| 35 |

|

| ns | ||

R/W | BUSY |

|

|

|

| |||||||||||||||||

tBDD[35] |

|

|

|

|

|

|

| HIGH to Data Valid |

|

| 30 |

|

| 40 | ns | |||||||

BUSY |

|

| ||||||||||||||||||||

Document #: | Page 15 of 26 |

[+] Feedback