|

|

|

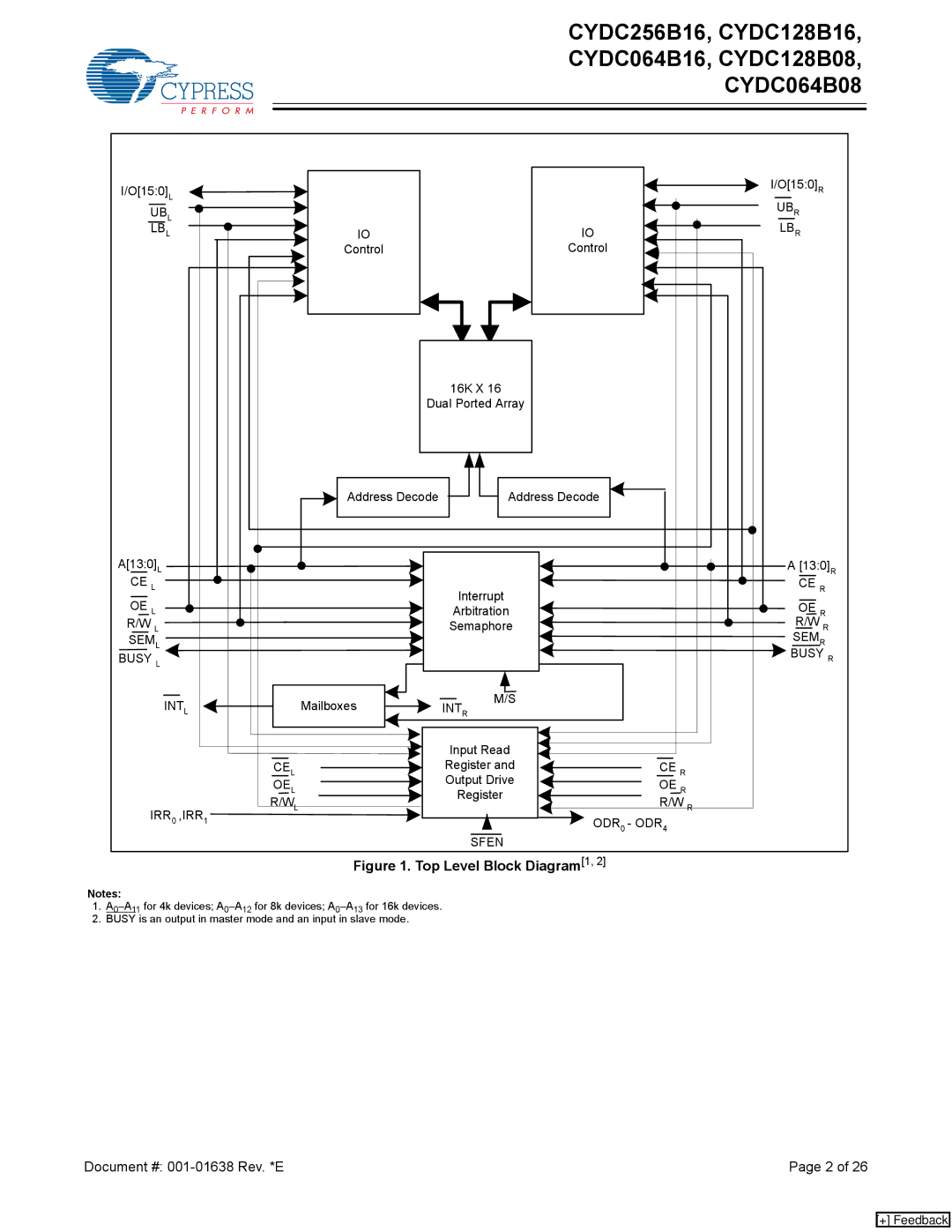

| CYDC256B16, CYDC128B16, | |

|

|

|

| CYDC064B16, CYDC128B08, | |

|

|

|

|

| CYDC064B08 |

I/O[15:0]L |

|

|

| I/O[15:0]R | |

|

|

| UBR | ||

UBL |

|

|

| ||

LBL | IO |

| IO | LBR | |

|

| Control |

| Control |

|

|

|

| 16K X 16 |

| |

|

| Dual Ported Array |

| ||

|

| Address Decode |

| Address Decode |

|

A[13:0]L |

|

|

| A [13:0]R | |

CE L |

| Interrupt | CE R | ||

OE L |

| OE R | |||

| Arbitration | ||||

R/W L |

| Semaphore | R/W R | ||

SEM | L |

|

|

| SEMR |

|

|

|

| BUSY R | |

BUSY L |

|

|

| ||

| INTL | Mailboxes | INT | M/S |

|

| R |

| |||

|

|

|

|

| |

|

|

| Input Read |

| |

|

| CEL | Register and | CE R | |

|

| OEL | Output Drive | OE R | |

|

| Register | |||

|

| R/WL | R/W R | ||

IRR0 ,IRR1 |

|

| |||

|

| ODR0 - ODR4 | |||

|

|

|

| ||

|

|

|

| SFEN |

|

Figure 1. Top Level Block Diagram[1, 2]

Notes:

1.

2.BUSY is an output in master mode and an input in slave mode.

Document #: | Page 2 of 26 |

[+] Feedback