CYDC256B16, CYDC128B16,

CYDC064B16, CYDC128B08,

CYDC064B08

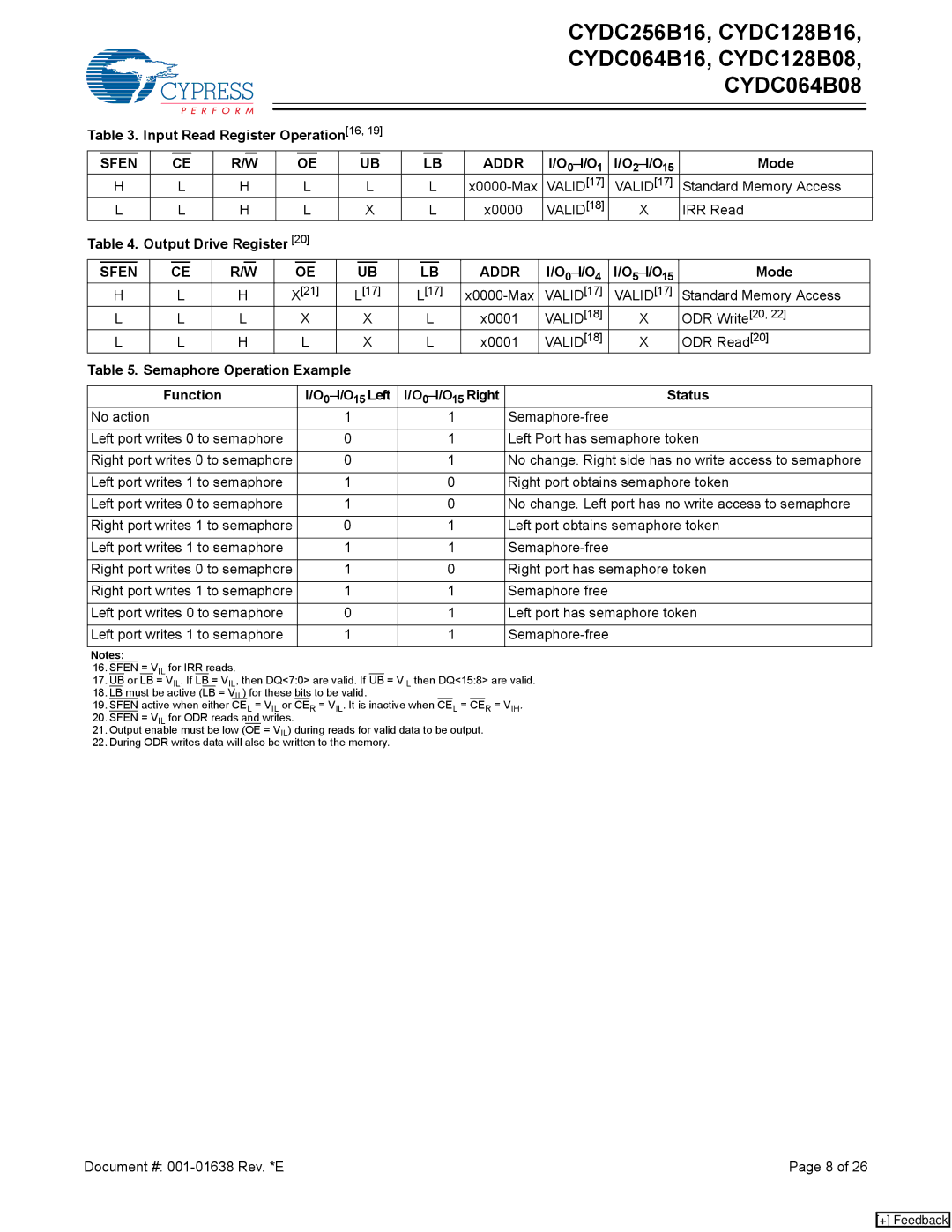

Table 3. Input Read Register Operation[16, 19]

| SFEN |

|

| CE |

| R/W |

| OE |

| UB |

| LB | ADDR |

|

| Mode | |||||||

| H |

|

| L |

| H |

| L |

| L |

| L | VALID[17] | VALID[17] | Standard Memory Access | ||||||||

| L |

|

| L |

| H |

| L |

| X |

| L | x0000 | VALID[18] | X | IRR Read | |||||||

Table 4. Output Drive Register [20] |

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

| SFEN |

|

| CE |

| R/W |

|

| OE |

|

| UB |

|

| LB |

|

| ADDR |

|

| Mode | ||

| H |

|

| L |

| H | X[21] | L[17] | L[17] |

| VALID[17] | VALID[17] | Standard Memory Access | ||||||||||

| L |

|

| L |

| L |

| X |

| X |

| L |

| x0001 |

| VALID[18] | X | ODR Write[20, 22] | |||||

| L |

|

| L |

| H |

| L |

| X |

| L |

| x0001 |

| VALID[18] | X | ODR Read[20] | |||||

Table 5. Semaphore Operation Example

Function |

| Status | |

No action | 1 | 1 | |

|

|

|

|

Left port writes 0 to semaphore | 0 | 1 | Left Port has semaphore token |

|

|

|

|

Right port writes 0 to semaphore | 0 | 1 | No change. Right side has no write access to semaphore |

|

|

|

|

Left port writes 1 to semaphore | 1 | 0 | Right port obtains semaphore token |

|

|

|

|

Left port writes 0 to semaphore | 1 | 0 | No change. Left port has no write access to semaphore |

|

|

|

|

Right port writes 1 to semaphore | 0 | 1 | Left port obtains semaphore token |

|

|

|

|

Left port writes 1 to semaphore | 1 | 1 | |

|

|

|

|

Right port writes 0 to semaphore | 1 | 0 | Right port has semaphore token |

|

|

|

|

Right port writes 1 to semaphore | 1 | 1 | Semaphore free |

|

|

|

|

Left port writes 0 to semaphore | 0 | 1 | Left port has semaphore token |

|

|

|

|

Left port writes 1 to semaphore | 1 | 1 | |

|

|

|

|

Notes: |

|

|

|

16.SFEN = VIL for IRR reads.

17.UB or LB = VIL. If LB = VIL, then DQ<7:0> are valid. If UB = VIL then DQ<15:8> are valid.

18.LB must be active (LB = VIL) for these bits to be valid.

19.SFEN active when either CEL = VIL or CER = VIL. It is inactive when CEL = CER = VIH.

20.SFEN = VIL for ODR reads and writes.

21.Output enable must be low (OE = VIL) during reads for valid data to be output.

22.During ODR writes data will also be written to the memory.

Document #: | Page 8 of 26 |

[+] Feedback