ATCA-9305ATCA Blade with Dual Cavium Processors

Revision Level Principal Changes Date

FCC Rules and Regulations Part

Regulatory Agency Warnings & Notices

EMC Compliance

GR-1089-CORE Standard

Product Atca Blade Model Name/Number

Manufacturer’s Name

Iii

Regulatory Agency Warnings & Notices

Contents

Ethernet Interface

Back Panel Connectors

Acronyms

Figures

Blank

Tables

Tables

Xiii

Xiv

Registers

Blank

Overview

Components and Features

Management Processor

Overview Components and Features

Functional Overview

Overview Functional Overview

Additional Information

Type Specification

Product Certification

Type

RoHS Compliance

EMC

Technical References

Terminology and Notation

Device Document Interface

RTC

Ipmi

Blank

Width Depth Height Weight typical

Setup

Electrostatic Discharge

ATCA-9305 Circuit Board

Setup ATCA-9305Circuit Board

Component Map, Top Rev

3Component Map, Bottom Rev

4LED, Fuse and Switch Locations, Top

5LED and Switch Locations, Bottom

Connectors

ATCA-9305 Setup

Configuration Header

IG ROM Redir EN Boot Stand Prog

Configuration Power

Power Requirements

Environmental Considerations

Environment Range Relative Humidity

7Air Flow Graph

Hot Swap

Technical Support

Troubleshooting

Insert a board

8Serial Number and Product ID on Top Side

Product Repair

Comments and Suggestions

Blank

Cavium CN5860 Processor

Feature Description

Rldram

PCI

Cavium Memory Map

Cavium Processor Complex PCI

PCI

Hex Physical Address Register Description

CN5860 Boot Over PCI

Cpld

Cavium Reset

Cavium Ethernet

Cavium Processor Complex Cavium Ethernet

00 80 F9 xx yy zz

Offset

Cavium Processor Complex Cavium Monitor

Power-up/Reset Sequence

Cavium Monitor

Start-up Display

Post Diagnostic Results

Diagnostic Tests During Power-up and Reset

Cavium Environment Variables

Diagnostic Bit Test Description Value

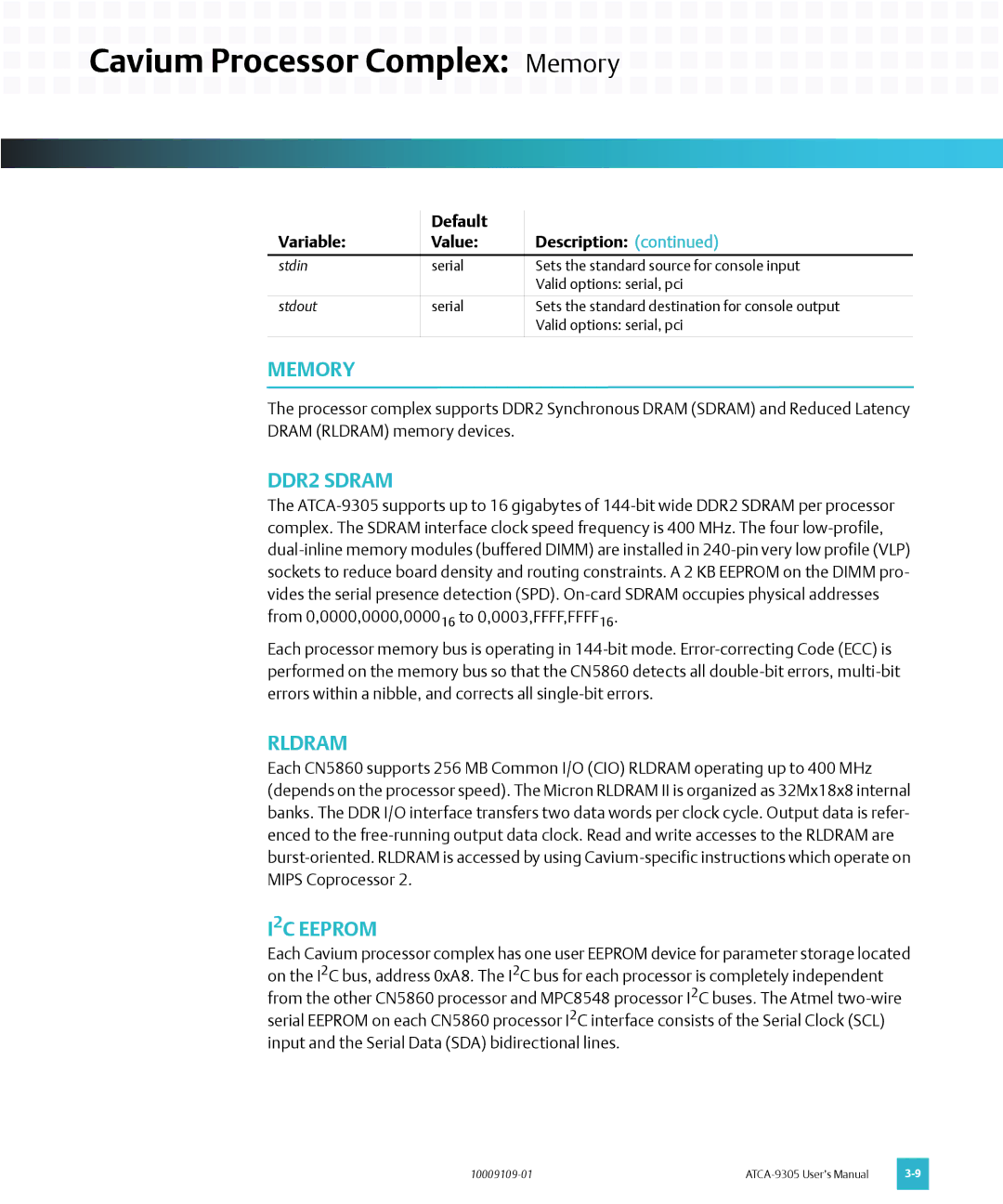

Memory

Cavium Processor Complex Memory

DDR2 Sdram

Rldram

Flash, 512 KB x

Cavium Processor Complex StratixGX Interconnect

Flash, 4 MB x

Stratixgx Interconnect

Register 3-2Data 2316

Control Register

Address Registers

Scratch Register

Version Register

Headers and Connectors

Cavium Processor Complex Headers and Connectors

COP/JTAG Headers

Pin J1 processor J15 processor

Pin

Console Serial Ports optional

Blank

RJ45

Management Complex

MPC8548 Processor

Management Complex MPC8548 Processor

MPC8548 Memory Map

Jtag

MPC8548 Ccsrbar 1MB

Hex Physical Access See Address Mode Register Description

Hex Physical

See Address Mode Register Description

LED

Chip Selects

Pin Signal

Sdram DDR2 2 GB

Ipmp Cpld

Reset Diagram

Sdram

Management Complex Memory

Flash

KB x 8 optional

PCI Express

Management Complex PCI

GB x

MB x

I2C Interface

Management Complex I2C Interface

Management Processor Header and Serial Port

JTAG/COP Interface optional

Serial Debug Port

MPC8548 PLD Register Summary

Management Processor Cpld

Address Offset hex Mnemonic Register Name See

Product ID

Management Processor Cpld MPC8548 PLD Register

Hardware Version

Bits Function Description

Hardware Configuration

PLL Reset Configuration

PLD Version

LED

Jumper Settings

Reset Command

Reset Event

Pqcr

WBR

CAV1CR

CAV2CR

Reset Command Sticky #1

Boot Device Redirection

Reset Command Sticky #2

Miscellaneous Control

Low Frequency Timer 1

RTM Gpio Control

RTM Gpio State

RTM Status

Frequency Set Register Comments

Cavium 2 Cmul Clock Divisor Control

Cavium 1 Cmul Clock Divisor Control

Cavium Gpio Control

Jtag

Cavium Gpio Data

Cavium Gpio Data Out

LPC Bus Control

IPMP/IPMC Gpio Control

LPC Data

Serial IRQ Interrupt

Blank

Ethernet Switching

Broadcom BCM56802 Switch

Ethernet Interface

Ethernet Switch Ports

Ethernet Interface Ethernet Switching

Ethernet Transceivers

Port Interface Connection

Ethernet Interface MPC8548 Management Processor Ethernet

Vlan Setup

MPC8548 Management Processor Ethernet Address

Ports

Front Panel Ethernet Ports

Pin P1 Signal P3 Signal

TSEC1CHSGND FP1CHSGND

Blank

Ipmc Overview

System Management

Ipmi Messaging

System Management Ipmi Messaging

OEM

Hex Code Values Name Type

Code Description

Ipmi Completion Codes

Ipmb Protocol

System Management Ipmb Protocol

Byte Bits

Sipl Protocol

System Management Sipl Protocol

Message Bridging

System Management Message Bridging

B0 xx 01

Standard Commands

System Management Standard Commands

Command NetFn

Cmd

Picmg

OEM Boot Options

System Management OEM Boot Options

Parameter Parameter Data

Ipmc Watchdog Timer Commands

System Management Ipmc Watchdog Timer Commands

Watchdog Timer Actions

Watchdog Timer Use Field and Expiration Flags

Using the Timer Use Field and Expiration Flags

Watchdog Timer Event Logging

Monitor Support for Watchdog Timer

Monitor Post Time-out

Set Watchdog Timer Command

Reset Watchdog Timer Command

Type Byte Data Field

9Set Watchdog Timer Command

Get Watchdog Timer Command

System Management Ipmc Watchdog Timer Commands

FRU Leds

System Management FRU LEDs

Reference LEDs Hex Designator Description

OOS

Get LED Color Capabilities Command

Get FRU LED Properties Command

LED ID

Response Data

Set FRU LED State Command

Function is FBh

Get FRU LED State Command

System Management FRU LEDs

Vendor Commands

System Management Vendor Commands

Get Status

Carrier controller

Get Serial Interface Properties

Set Serial Interface Properties

Set Debug Level

Get Debug Level

Set Hardware Address

Get Hardware Address

Set Handle Switch

Get Handle Switch

Get Payload Communication Time-Out

Enable Payload Control

Set Payload Communication Time-Out

Reset Ipmc

Disable Payload Control

Hang Ipmc

Bused Resource Status

Bused Resource

Graceful Reset

Get Payload Shutdown Time-Out

Diagnostic Interrupt Results

Set Payload Shutdown Time-Out

Set Local FRU LED State

Get Local FRU LED State

Update Threshold Sensor

Update Discrete Sensor

Boot Device Redirection BDR

System Management Boot Device Redirection BDR

4Boot Device Diagram

Payload Reset Indication Clear

Payload Reset Indication

System Management Message Listeners

Message Listeners

Remove Message Listener

Add Message Listener

Get Message Listener List

System Management System Firmware Progress Sensor

System Firmware Progress Sensor

Entities and Entity Associations

System Management Entities and Entity Associations

Sdram Post

Sensor Event Reading Enity Entity Name Type Instance Gen

Sensors and Sensor Data Records

Sdram Post

Post

Byte Field Description

FRU Inventory

System Management FRU Inventory

Keying

System Management E-Keying

HPM.1 Firmware Upgrade

System Management HPM.1 Firmware Upgrade

Base Point-to-Point Connectivity

Field Value Description

Pin Signal Direction

HPM.1 Reliable Field Upgrade Procedure

System Management Ipmc Headers

Ipmc Headers

Blank

Pin Signal Insertion Sequence

Back Panel Connectors

Zone

Enableb

Back Panel Connectors Zone

Enable a

P10CHSGND

Row Interface

Ipmbrtmsdabuff 33VMPRTM

Rtmrst

12VRTM

Management Processor Monitor

COMMAND-LINE Features

LED Code Power-up Status LED Value

Management Processor Monitor Command-Line Features

Boardpreinit

Serialinit

Basic Operation

Management Processor Monitor Basic Operation

2Power-up/Reset Sequence Flowchart

Post Diagnostic Results

Monitor Recovery and Updates

Management Processor Monitor Monitor Recovery

Bit Diagnostic Test Description Value

Monitor Sdram Usage

Resetting Environment Variables

Recovering the Monitor

Updating the Monitor via Tftp

Address Range hex Device

Monitor Command Reference

Management Processor Monitor Monitor Command

Command Syntax

Boot Commands

Management Processor Monitor Boot Commands

Bootvx

Bootv

Dhcp

Tftpboot

Rarpboot

File Load Commands

Management Processor Monitor File Load Commands

Memory Commands

Loadb

Cmp

Management Processor Monitor Memory Commands

Find

Example

Definition

Flash Commands

Management Processor Monitor Flash Commands

Erase

Flinfo

EEPROM/I2C Commands

Management Processor Monitor EEPROM/I2C Commands

Protect

Eeprom

Iloop

Icrc32

Imd

Imm

Ipmc Commands

Management Processor Monitor Ipmc Commands

Bootdev

Iprobe

Fruled

Fruinit

Ipmchpmfw

Sensor

Management Processor Monitor Environment Parameter

Environment Parameter Commands

Printenv

Saveenv

Test Commands

Management Processor Monitor Test Commands

Other Commands

Management Processor Monitor Other Commands

Iminfo

Help

Isdram

Loop

Phy

Pci

Ping

Reset

Run

Script

Sleep

Switchreg

Version

Vlan

MPC8548 Environment Variables

Management Processor Monitor MPC8548 Environment

Atca

Download Formats

Management Processor Monitor Troubleshooting

9600 bps, no parity, 8 data bits, 1 stop bit

Binary

Management Processor Monitor Download Formats

Motorola S-Record

Blank

GbE

Acronyms

SPI-4.2

PCIe

Air flow rate

Index

Index

Watchdog timer

Blank

10009109-01

E R S O N. C O N S I D E R I T S O L V E D