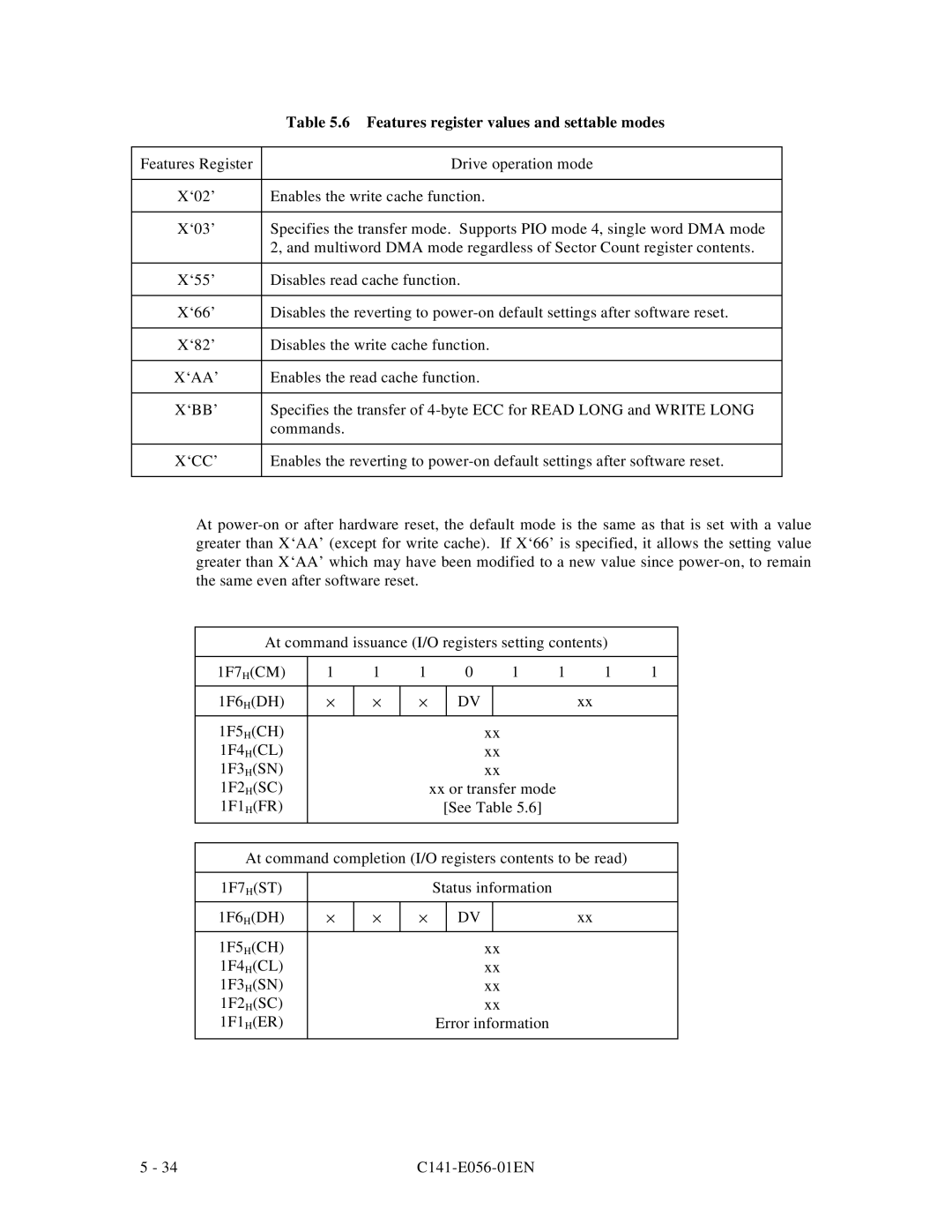

| Table 5.6 Features register values and settable modes |

|

|

Features Register | Drive operation mode |

|

|

X‘02’ | Enables the write cache function. |

|

|

X‘03’ | Specifies the transfer mode. Supports PIO mode 4, single word DMA mode |

| 2, and multiword DMA mode regardless of Sector Count register contents. |

|

|

X‘55’ | Disables read cache function. |

|

|

X‘66’ | Disables the reverting to |

|

|

X‘82’ | Disables the write cache function. |

|

|

X‘AA’ | Enables the read cache function. |

|

|

X‘BB’ | Specifies the transfer of |

| commands. |

|

|

X‘CC’ | Enables the reverting to |

|

|

At

At command issuance (I/O registers setting contents)

1F7H(CM) | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | ||

|

|

|

|

|

|

|

|

|

|

|

1F6H(DH) | × | × | × |

| DV |

|

|

| xx |

|

|

|

|

|

|

|

|

|

|

|

|

1F5H(CH) |

|

|

|

|

| xx |

|

|

| |

1F4H(CL) |

|

|

|

|

| xx |

|

|

| |

1F3H(SN) |

|

|

|

|

| xx |

|

|

| |

1F2H(SC) |

|

|

| xx or transfer mode |

|

|

| |||

1F1H(FR) |

|

|

| [See Table 5.6] |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

At command completion (I/O registers contents to be read)

1F7H(ST) |

|

|

| Status information |

| ||

|

|

|

|

|

|

|

|

1F6H(DH) | × | × | × |

| DV |

| xx |

|

|

|

|

|

|

|

|

1F5H(CH) |

|

|

|

| xx |

| |

1F4H(CL) |

|

|

|

| xx |

| |

1F3H(SN) |

|

|

|

| xx |

| |

1F2H(SC) |

|

|

|

| xx |

| |

1F1H(ER) |

|

|

| Error information |

| ||

|

|

|

|

|

|

|

|

5 - 34 |