Page

AN/USM-459 HEWLETT-PACKARD Model 5328A/E42 NSN

Page

I b l a n k

TM 11-6625-2941-14 + P

Page

Installation

Table of Contents

Theory of Operation

Model 5328A Table of Contents

Vll

Table of Contents Section

L l

Appendix A. References

List of Figures

Model 5328A List of Tables

List of Tables

Vii

Remote Controllable Programmable Input Block Diagram

Service

Model 5328A Safety Considerations

F E T Y C O N S I D E R a T I O N S General

Operation

Model 5328A Safety Considerations

Model 5328A 500 MHz Universal Frequency Counter

Model 5328A General Information

Section O Introduction

Administrative Storage

Indexes of Publications

Forms and Records

Page

C T I O N N E R a L I N F O R M a T I O N Scope of Manual

Model 5320A General Information

Description

Instrument Identification

Equipment Supplied

Accessories Available

Programmable Operation Channels a and B

5328A Counter Specifications

Channel C Time Base

A Counter Specifications

Trigger level 0 volts

Maximum Input 5 volts rms

Preparation for USE

C T I O N I Installation

Unpacking and Inspection

Bench Operation

Operating Environment

Rack Mounting

Packaging for Reshipment

Storage

Model 5328A Installation Other Packaging Methods

Page

E R a T I O N

Model 5328A Operation C T I O N I l l

E R a T O R S I N S T R U C T I O N S N T R O D U C T I O N

Frequency Measurements

Period Measurements

Model 5328A Operation

Deadtime

Time Interval Measurements

Operating Controls

Ratio Measurements

5328A Front Panel Operation Summary

A Front Panel Operation Summary

5328A Rear Panel Controls and Connectors

Function of CONTROLS, INDICATORS, INPUTS, and Outputs

Functions and Resolution Switch Settings

Model 5328A Operation Input Channel Section

B Channel Signal Conditioning

T E

Slope Switch Settings

Channel Overload lndicator

Model 5328A Operation Channel C Input

Hysteresis Band of Trigger Levels

External Frequency Standard Input

Setting Address Switches

Addresssing

Program Code Set

Model 5320A Operation

Measurement Output Format

BUS Commands

American Standard Code for Information Interchange Ascii

Program Examples

Model 5328A Operation

Page

C T I O N I E O R Y O F O P E R a T I O N

Model 5328A Theory of Operation

Overall Description

Basic Counter Operation

Measuring Period

Period

Time Interval

Time INTERVAL, RESOLUTION, and Averaging Techniques

Model 5328A Theory of Operation Ratio

Time Interval Averaging

Model 5328A Theory of Operation Resolution

36.±1 Count Ambiguity

Sources of Measurement Error

Trigger Error

Time Base Error

Main Counter Section

48.5328A Principles of Operation

Block Diagram

2 . a 1 M O T H E R B O a R D

Input Section

Hewlett-Packard Interface Bus HP-US Section

69.A3 Oscillator Support

Decade Counting Assembly DCA

85.+5V Supply

83.A2 Power Supply

Arming Multiplexer and Arming FF

89.A4 Function Selector

High Speed Multiplexer, Main Gate, and 1st Decade

An Example of Operation

103.A16 Display Assembly

Remote Controllable Programmable Input Block Diagram

Function

5328A Input Circuit Program Code Set

Examples

122.A12 Amplifier Board

Remote Controllable Programmable Input Schematic Theory

117.A19 Switch Control Board

127.A10 Synchronizer Board

Model 5328A Theory of Operation

147.A11 DAC Board

HP Interface BUS Theory

156.A8 Channel C Input

HP-IB A15 Interface Operation

Listen Mode

Bus Command Mode

Talk Mode

Model 5328A Theory of Operation Overall Operation

Model 5328A Theory of Operation

10.ASM Oscillator Timing Diagram

Assembly Connection Identification

Assembly Designations

C T I O N I N T E N a N C E

Test Equipment

Preventive Maintenance

Model 5328A Maintenance Recommended Test Equipment

Preventive Maintenance

Cleaning

Model 5328A Maintenance Inspection

Repair Printed Circuit Component Replacement

Performance Test

Performance Test

Sensitivity Channel a Specification

Setup

Sensitivity Channel B Specification

Model 5328A Maintenance Performance Test

Signal Generator HP 5328A Channel C

SENSITIVITY-Channel C Specification

Setup HP 8840A

Ratio B/A, or C/A Specification

Time Interval and Time Interval Average

GATE/MARKER OUT and Sample Rate Setup

Remote Programming Test Setup

Performance Test

Performance Test

Atten X1 Test

Tab/e 5-4. Performance Test

Atten X10 Test

Atten X100 Test

Remote Trigger Level Test Setup

Performance Test

Performance Test

Page

17A

Performance Check Test Card

Test Description Results Pass Fail

Page

Test Description Results Pass Fail Ratio B/A

5328A Date

GATE/MARKER OUT and Sample Rate Remote Programming

17B

Page

Sensitivity Adjustments

Adjustments

Model 5328A Maintenance

Model 5328A Maintenance

DAC Adjustment Equipment Connections

DAC Adjustment oscilloscope readout and adjustment locations

7 . Troubleshooting

Model 5328A Maintenance Adjustment of A3 Oscillator Support

Troubleshooting Aids

Extender Board

A3 Jittler Adjustment

Function Signals

Model 5328A Maintenance IC Troubleshooting

5IC Troubleshooting, A1 Motherboard

IC Troubleshooting, A1 Motherboard

IC Troubleshooting, A1 Motherboard

HP-IB Verification Using the HP9825A

LC Troubleshooting, A1 Motherboard 5328A Functional Signals

System Configuration

Sample Printout

Program Listing

Program Listing

Program Listing

8A. Program Description

Step Test Counter Display Readout

8B. Program Description

8C. HP-IR Bus Commands

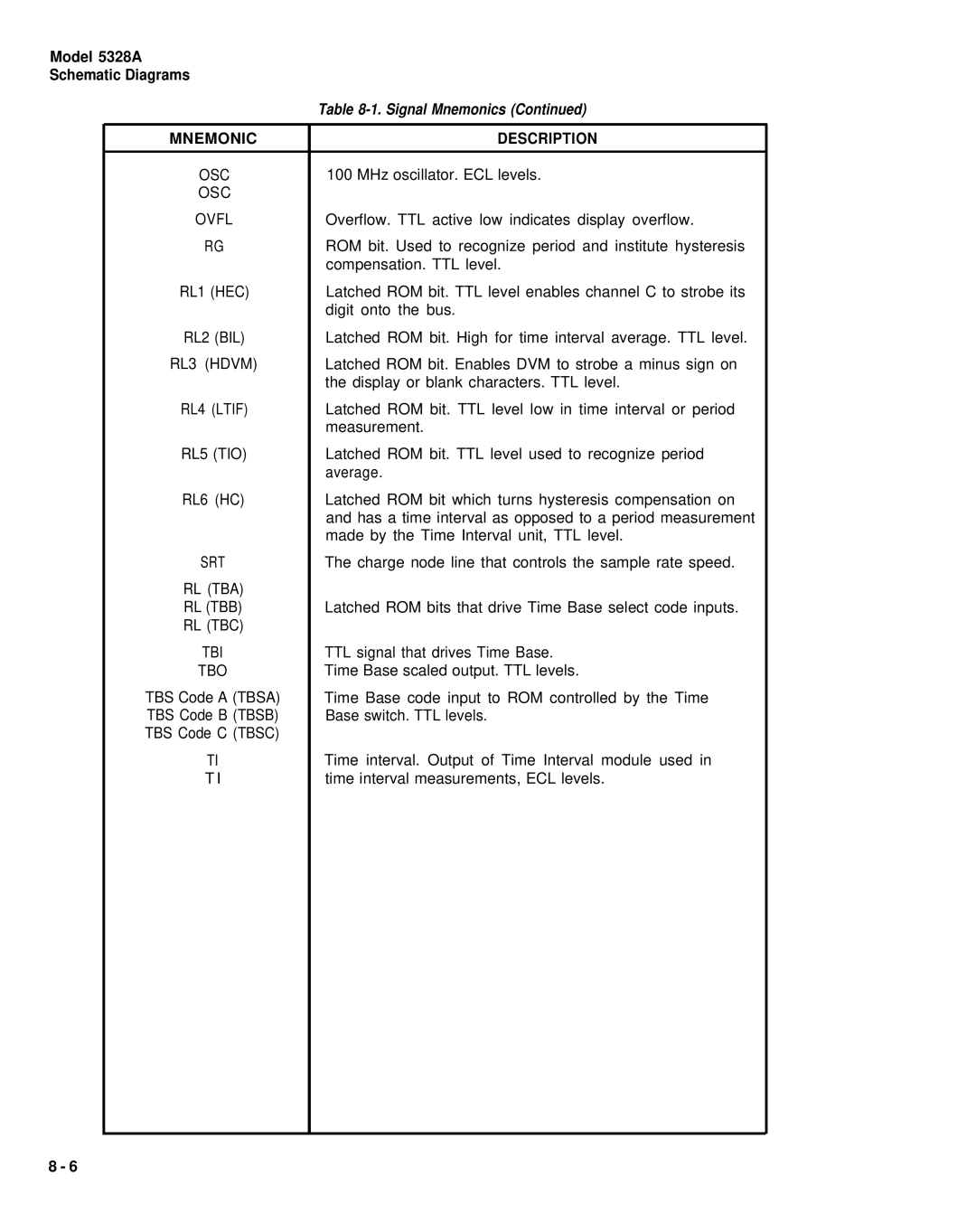

5328A A15 Qualifiers and Signal Mnemonics

Outputs

A A15 Qualifiers and Signal Mnemonics

Signal Source Description

11.Relay Control Logic

Troubleshooting Input Channels

10.A12 Relay Operation

Model 5328A Maintenance

Model 5328A Maintenance

Page

Instrument Cover Removal

Removal and Replacement Instructions

60Display Assembly Removal and Replacement

Model 5328A Maintenance

10. Assembly Flowchart Sheet 1

10. Assembly Flowchart Sheet 2

10. Assembly Flowchart Sheet 3

11.Local Troubleshooting Flowchart Sheet 1

11. Address Switch Troubleshooting Flowchart

12. Address Switch Troubleshooting Flowchart

R D E R I N G I N F O R M a T I O N

Model 5328A Replaceable Parts

C T I O N V P L a C E a B L E P a R T S

Model 5328A Replaceable Parts

Prefix Component/Part/Material

HP Part Number Organization

Component Parts and Materials

Part Number to National Stock Number Cross Reference Index

Factory Selected Parts

DIODE-SWITCHING 30V 50MA 2NS DO-35

DIODE-SWITCHING 80V 200MA 2NS DO-35

Mother Main BOARD, Series

Not Assigned

NETWORK-RES 9-ON-SIP .15-PIN-SPCG

SWITCH-SL DPDT-NS Submin .5A 125VAC PC

IC Cntr TTL Decd Synchro POS-EDGE-TRIG

IC SCHMITT-TRIG TTL Nand Quad 2-INP

CONNECTOR-PC Edge 18-CONT/ROW 2-ROWS

CONNECTOR-SGL Xont PIN .04-IN-BSC-32 RND

CONNECTOR-PC Edge 15-CONT/ROW 2-ROWS

ASSEMBLY,POWER Supply Series

Crystal Oscillator Assembly

Connector 3-PIN F

Fuse 2A 250V FAST-BLO 1.25X.25 UL IEC

Inductorfxd 300UH AT 5A DC

Cable ASSEMBLY, Oscillator

DIODE-SWITCHING 30V 50MA 2NS D0-35

CONNECTOR-RF SMC FEM Unmtd 50-OHM

CONNECTOR-RF BNC FEM SGL-HOLE-RR 50-OHM

CAPACITOR-FXD 60PF +-5% 300VDC Mica

CAPACITOR-FXD 800PF +-1% 300VDC Mica

CAPACITOR-FXD 15PF +-5% 500VDC Mica

NETWORK-RES 9-PIN 81P .15-PIN-SPCG

Connector ASSEMBLY,SMC

Connector ASSEMBLY, BNC

Channel Input Series

CAPACITOR-FXD 68UF+-20% 6VDC TA

Resisto

RESISTOR-TRMR 10K 10% C SIDE-ADJ 1-TRN

Cable ASSEMBLY, Test

Cable ASSEMBLY, Frequency C

CABLE, Overload Indicator

CONNECTOR-SGL Cont SKT RND

CONNECTOR-SGL Cont PIN .04-IN-SBC-8Z RND

SWITCH-SL DPDT-NS Mintr 1A 125VAC PC

CONNECTOR-SGL Cont PIN .04-IN-BSC-8Z NRD

CONNECTOR-SGL Cont PIN .04-IN-BSC-SZ RND

DIODE-SWITCHING 15V 50MA 750PS D0-7

DIODE-SWITCHING 15V 50MA 750PS DO-7

Transistor J-FET N-CHAN D-MODE SI

Transistor J-FET P-CHAN D-MODE SI

CONNECTOR-SGL Cont PIN .04-IN-BSC-8Z RNS

CONNECTOR-SGL Cont PIN .04-IN-BSC-8Z RND

Cable ASSEMBLY, RF/A & B Input

CONNECTOR-RF FEM SGL-HOLE-RR 50-OHM

CAPACITOR-FXD 10UF+-20% 25VDC TA

DIODE-SWITCHING 30V 50MA 2NA DO-35

CAPACITOR-FXD 470PF +-20% 500VDC CER

CAPACITOR-FXD 3.3PF +-.25PF 500VDC CER

RESISTOR-TRMR 100 10% C SIDE-ADJ 1-TRN

RESISTOR-TRMR 100 10% C SIDE-ADJ 1=TRN

IC Gate ECL EXCL-OR/NOR TPL 1-INP

IC Comparator 16-DIP-C

SWITCH-SL 7-1A-NS DIP-NS DIP-SLIDE-ASSY .1A

Connector 24-PIN F Microribbon

CAPACITOR-FXD 33UF+-10% 10VDC TA

NETWORK-RES 10-PIN-SIP .1-PIN-SPCG

Display Assembly

Cable ASSEMBLY, HP-IB Single

DIODE-SWITCHING 30V 50MA 2NS DO.35

IC LCH TTL L D-TYPE 4-BIT

SWITCH-PB Dpdt MOM .02A 20VAC

SWITCH-TGL Submin Dpdt NS 2A 250VAC PC

CONNECTOR-SGL Cont PIN 1.143MM3BSC-SZ SQ

CONNECTOR-PC Edge 24-CONT/ROW 2-ROWS

LED, Indicator

SWITCH-SL DP3T-NS Mintr .5A 125VAC/DC PC

Cable ASSEMBLY,OVERLOAD

A19 Miscellaneous

SWITCH-SL DPDT-NS STD 1.5A 250VAC

FAN and Control Module Assembly

CONNECTOR-RF BNC FEM SGL-HOLE-FR 50-OHM

Cover Assembly

Manufacturers Code list

73899 5910-00-983-2623

0757-0280 28480 5905-00-853-8190

2100-1738 28480 5905-00-256-8993

Page

Manual Changes Sheet

Model 5328A Manual Changes

C T I O N V I N U a L C H a N G E S

Change Date July 7

N U a L D E S C R I P T I O N

Manual Changes Model 5328A/H42

Page

Identification Markings on Printed Circuit Boards

Schematic Diagram Symbols and Reference Designators

H E M a T I C D I a G R a M S

Assembly Locations and Component Locators

Model 5328A Schematic Diagrams

Aoro

Identifies

Schematic Diagram Notes

Mnemonic Description

Signal Mnemonics

ARM

DVM

RL IA

Htbo

RL IC ANN

Lddca

RL5 TIO

OSC

RL3 Hdvm

5328A Front View

5328A Top View

5328A Bottom View

Page

A1 Motherboard

7.A1 Mother board Assembly

7.A1 Motherboard Assembly

7.A1 Motherboard Assembly

A1 Motherboard Schematic and Components Sheet 1

A1 Motherboard Schematic and Components Sheet 2

A2 Power Supply Block Diagram

A2 Power Supply Schematic and Components

10.A3/A3A1 Oscillator Support Schematic and Components

10.A3/A3A1 Oscillator Support Schematic and Components

11.A4 Function Selector Block Diagram

12.A4 Function Selector Assembly

12.A4 Function Selector Schematic and Components

13. A8 Channel C Block Diagram

14.A8 Channel CSchematic and Components

15.A10 Synchronizer Block Diagram

16.A10 Synchronizer Schematic and Components

17. A11 Digital-to-Analog Converter Block Diagram

18.A11 Digital-to-Analog Converter Schematic and Components

19. A12 A-B Channel Block Diagram

20.A12 A-B Channel Schematic and Components

21.A15 HP-IB Interface Block Diagram

22.A15 HP-IB Interface Schematic and Components

22.A15 HP-IB Interface Schemaatic and Components

23.A16 Display Block Diagram

Page

24.A16 Display Schematic and Components

25.A19 Switch/Attenuator Schematic and Components

Appendix a References

Page

Section I. Introduction Scope

P E N D I X B M P O N E N T S O F E N D I T E M L I S T

General

Explanation of Columns

Cover Assembly Inside Cover

Power Cord Inside Cover

Counter Electronic Digital Readout

Extender Board Inside Cover

Section Basic Issue Items Illustration National

Page

P E N D I X D I N T E N a N C E a L L O C a T I O N

Maintenance Function

Section l. Introduction General

Column Entries

Remarks Sec

Tool and Test Equipment Requirements Sec Ill

Electronic Counter AN/USM-459

Signal Generator HP 608 CR

Signal Generator SG-1112V1/U

Power Supply PP-7547/U HP 6113A Voltmeter HP

Repair KIT Printed Wiring Board MK-772/U

Section IV. Remarks

Page

By Order of the Secretary of the Army

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

Page

PIN