SYSTEM 0BJECrS STRUCl'URES

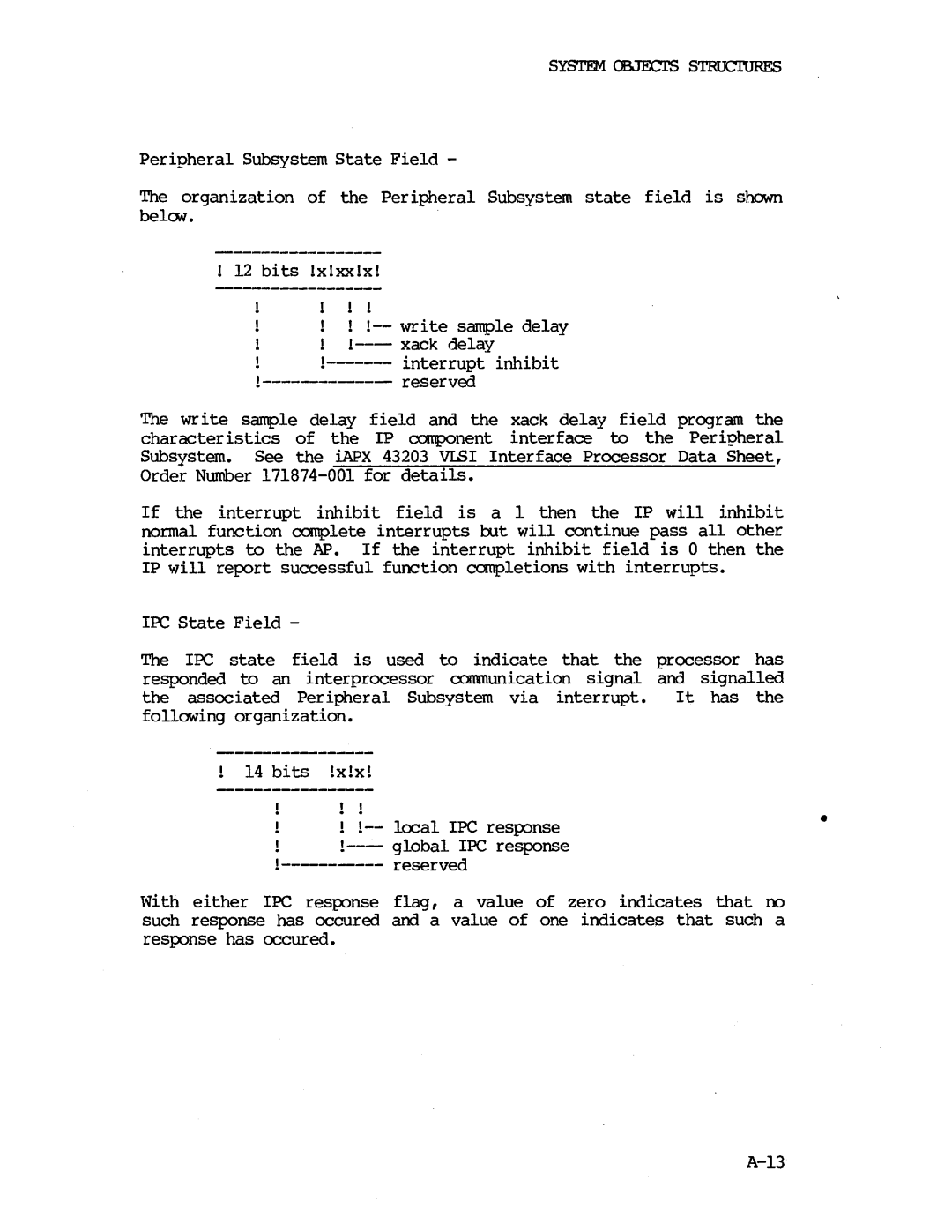

Peripheral Subsystem State Field -

The organization of the Peripheral Subsystem state field is shown

belCM.

1 12 bits lxlxxlxl

|

| 1 | 1 |

|

| 1 | |

| ! | ||

1 | 1 | interrupt inhibit | |

| reserved | ||

The write sample delay field and the xack delay field program the characteristics of the IP conponent interface to the Peripheral Subsystem. See the iAPx 43203 VI..SI Interface Processor Data Sheet, Order Number

If the interrupt inhibit field is a 1 then the IP will inhibit normal function complete interrupts but will continue pass all other interrupts to the AP. If the interrupt inhibit field is 0 then the IP will report successful function completions with interrupts.

IPC State Field -

The IPC state field is used to indicate that the processor has responded to an interprocessor conmunication signal and signalled

the associated Peripheral Subsystem via interrupt. It has the following organization.

14 bits lxlxl

1 | 1 | • |

1 | ||

1

1

With either IPC response such response has occured response has occured.

flag, a value of zero indicates that 00 and a value of one indicates that such a