LAPX 432 Interface Processor Architecture Reference Manual

3-3. RANOOM mOE DATA TRANSFER

Given that an IP address reference has passed the consistency checks, the IP finishes the Peripheral Subsystem bus cycle just as a menory oomponent would, accepting data from the bus in a wr i te operation, and placing data on the bus in a read operation.

It follCMS from the preceding discussion of transfer displacement computation that random mode transfers are always between corresponding relative locations of the windowed subrange and the windowed object. That is, the displacement of a transferred byte or double-byte is identical within the windowed object and the windowed subrange. For example, assume a PS subrange of 128 bytes at base address 4096 mapped onto a 432 object 100 bytes long with a base displacement of O. If a Peripheral Subsystem bus master initiates a bus cycle that decodes as "read one byte from location 4096", the IP will return the object byte whose displacement is zero, the first byte in the object. If a subsequent bus cycle indicates "write a double-byte into location 4100" , then the IP will accept a double-byte from the bus and write it into the object at a di.splacement of four. If another bus cycle attempts to "read one byte from lccation 4197", the IP will fault and will not perform the transfer, since the subrange transfer displacement exceeds the bounds of the object.

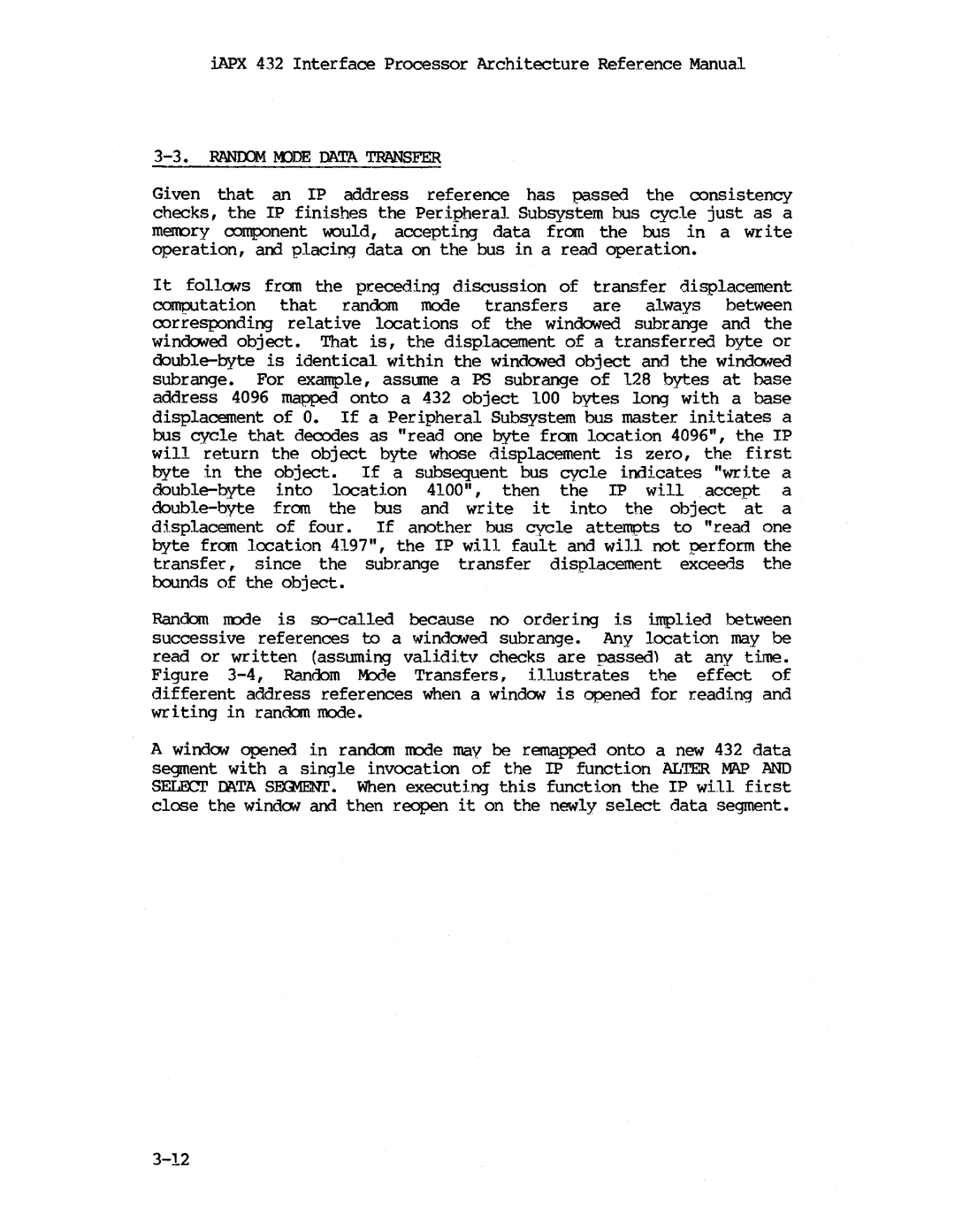

Random node is so-called because no order ing is implied between successive references to a windowed subrange. Any location may be read or written (assuming validitv checks are passed) at any time. Figure 3-4, Random ~e Transfers, illustrates the effect of different address references when a window is opened for reading and wr i ting in random mode.

A window opened in random node may be remapped onto a new 432 data segment with a single invocation of the IP function ALTER MAP AND SELECr MTA SEXNENl'. When executing this function the IP will first close the window and then reopen it on the newly select data segment.