Intel® PXA27x Processor Family Power Requirements

3.0Intel® PXA27x Processor Low Power Operating Modes

The PXA27x processor provides several

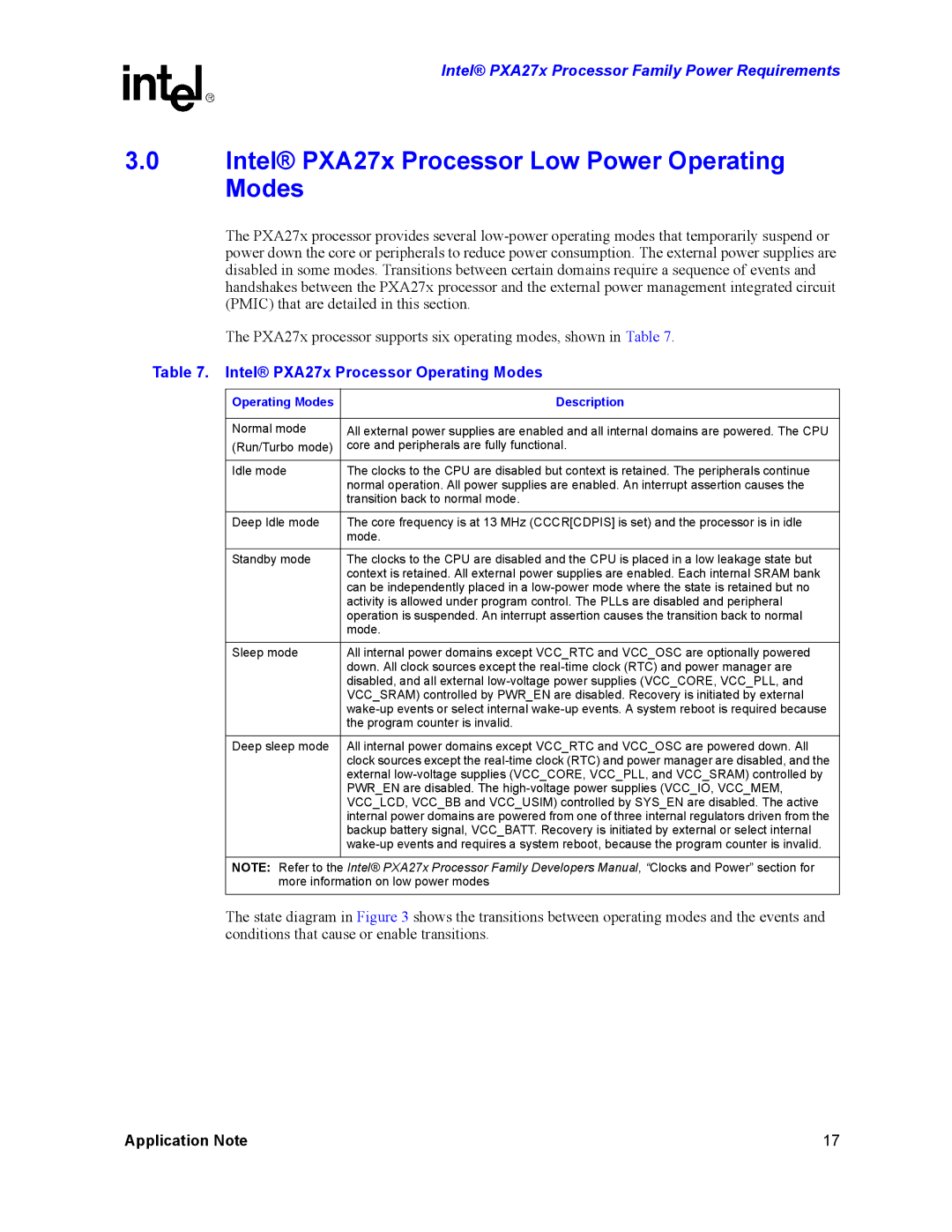

The PXA27x processor supports six operating modes, shown in Table 7.

Table 7. Intel® PXA27x Processor Operating Modes

Operating Modes | Description |

|

|

Normal mode | All external power supplies are enabled and all internal domains are powered. The CPU |

(Run/Turbo mode) | core and peripherals are fully functional. |

|

|

Idle mode | The clocks to the CPU are disabled but context is retained. The peripherals continue |

| normal operation. All power supplies are enabled. An interrupt assertion causes the |

| transition back to normal mode. |

|

|

Deep Idle mode | The core frequency is at 13 MHz (CCCR[CDPIS] is set) and the processor is in idle |

| mode. |

|

|

Standby mode | The clocks to the CPU are disabled and the CPU is placed in a low leakage state but |

| context is retained. All external power supplies are enabled. Each internal SRAM bank |

| can be independently placed in a |

| activity is allowed under program control. The PLLs are disabled and peripheral |

| operation is suspended. An interrupt assertion causes the transition back to normal |

| mode. |

|

|

Sleep mode | All internal power domains except VCC_RTC and VCC_OSC are optionally powered |

| down. All clock sources except the |

| disabled, and all external |

| VCC_SRAM) controlled by PWR_EN are disabled. Recovery is initiated by external |

| |

| the program counter is invalid. |

|

|

Deep sleep mode | All internal power domains except VCC_RTC and VCC_OSC are powered down. All |

| clock sources except the |

| external |

| PWR_EN are disabled. The |

| VCC_LCD, VCC_BB and VCC_USIM) controlled by SYS_EN are disabled. The active |

| internal power domains are powered from one of three internal regulators driven from the |

| backup battery signal, VCC_BATT. Recovery is initiated by external or select internal |

| |

|

|

NOTE: Refer to the Intel® PXA27x Processor Family Developers Manual, “Clocks and Power” section for more information on low power modes

The state diagram in Figure 3 shows the transitions between operating modes and the events and conditions that cause or enable transitions.

Application Note | 17 |