Intel® PXA27x Processor Family Power Requirements

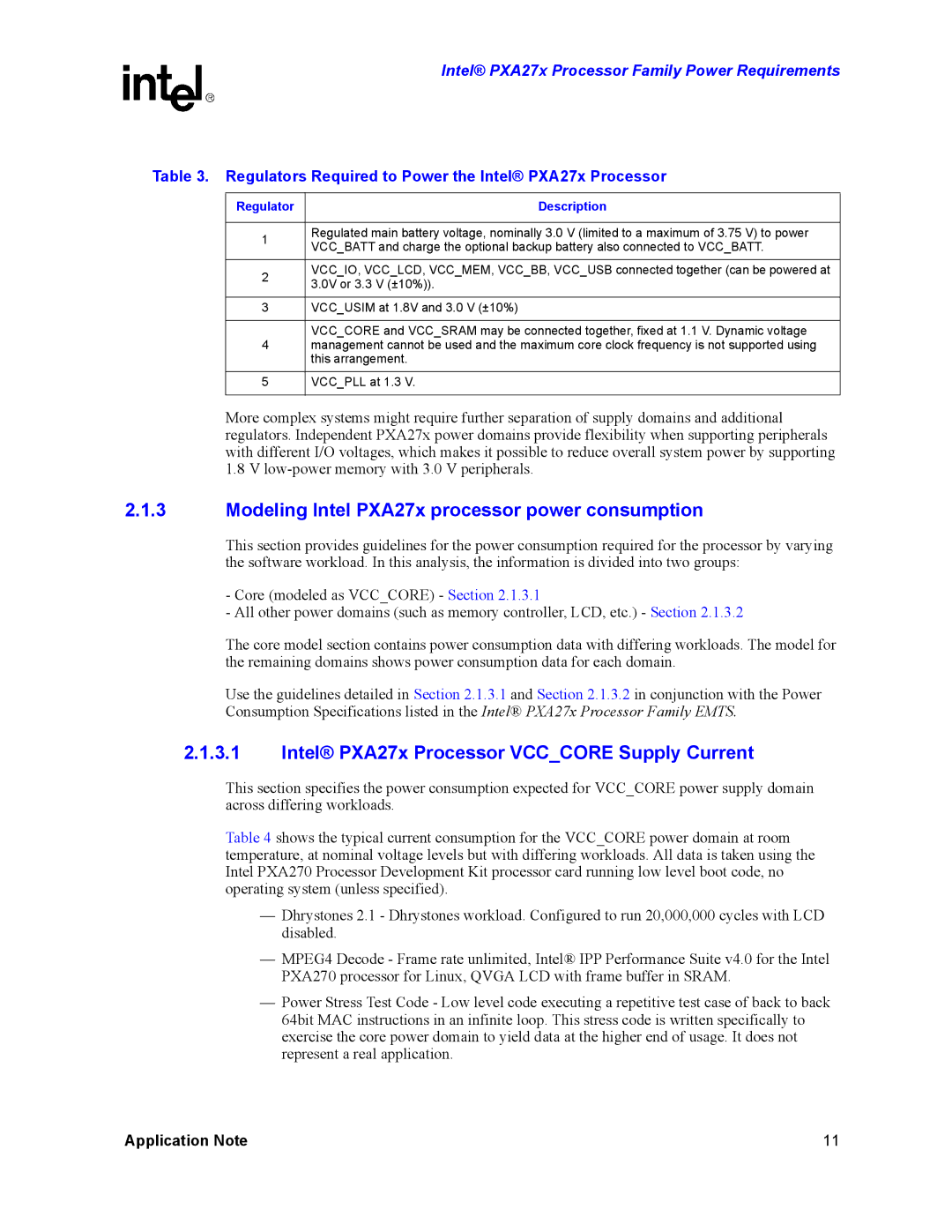

Table 3. Regulators Required to Power the Intel® PXA27x Processor

Regulator | Description | |

|

| |

1 | Regulated main battery voltage, nominally 3.0 V (limited to a maximum of 3.75 V) to power | |

VCC_BATT and charge the optional backup battery also connected to VCC_BATT. | ||

| ||

|

| |

2 | VCC_IO, VCC_LCD, VCC_MEM, VCC_BB, VCC_USB connected together (can be powered at | |

3.0V or 3.3 V (±10%)). | ||

| ||

|

| |

3 | VCC_USIM at 1.8V and 3.0 V (±10%) | |

|

| |

| VCC_CORE and VCC_SRAM may be connected together, fixed at 1.1 V. Dynamic voltage | |

4 | management cannot be used and the maximum core clock frequency is not supported using | |

| this arrangement. | |

|

| |

5 | VCC_PLL at 1.3 V. | |

|

|

More complex systems might require further separation of supply domains and additional regulators. Independent PXA27x power domains provide flexibility when supporting peripherals with different I/O voltages, which makes it possible to reduce overall system power by supporting

1.8 V

2.1.3Modeling Intel PXA27x processor power consumption

This section provides guidelines for the power consumption required for the processor by varying the software workload. In this analysis, the information is divided into two groups:

-Core (modeled as VCC_CORE) - Section 2.1.3.1

-All other power domains (such as memory controller, LCD, etc.) - Section 2.1.3.2

The core model section contains power consumption data with differing workloads. The model for the remaining domains shows power consumption data for each domain.

Use the guidelines detailed in Section 2.1.3.1 and Section 2.1.3.2 in conjunction with the Power Consumption Specifications listed in the Intel® PXA27x Processor Family EMTS.

2.1.3.1Intel® PXA27x Processor VCC_CORE Supply Current

This section specifies the power consumption expected for VCC_CORE power supply domain across differing workloads.

Table 4 shows the typical current consumption for the VCC_CORE power domain at room temperature, at nominal voltage levels but with differing workloads. All data is taken using the Intel PXA270 Processor Development Kit processor card running low level boot code, no operating system (unless specified).

—Dhrystones 2.1 - Dhrystones workload. Configured to run 20,000,000 cycles with LCD disabled.

—MPEG4 Decode - Frame rate unlimited, Intel® IPP Performance Suite v4.0 for the Intel PXA270 processor for Linux, QVGA LCD with frame buffer in SRAM.

—Power Stress Test Code - Low level code executing a repetitive test case of back to back 64bit MAC instructions in an infinite loop. This stress code is written specifically to exercise the core power domain to yield data at the higher end of usage. It does not represent a real application.

Application Note | 11 |