Intel® PXA27x Processor Family Power Requirements

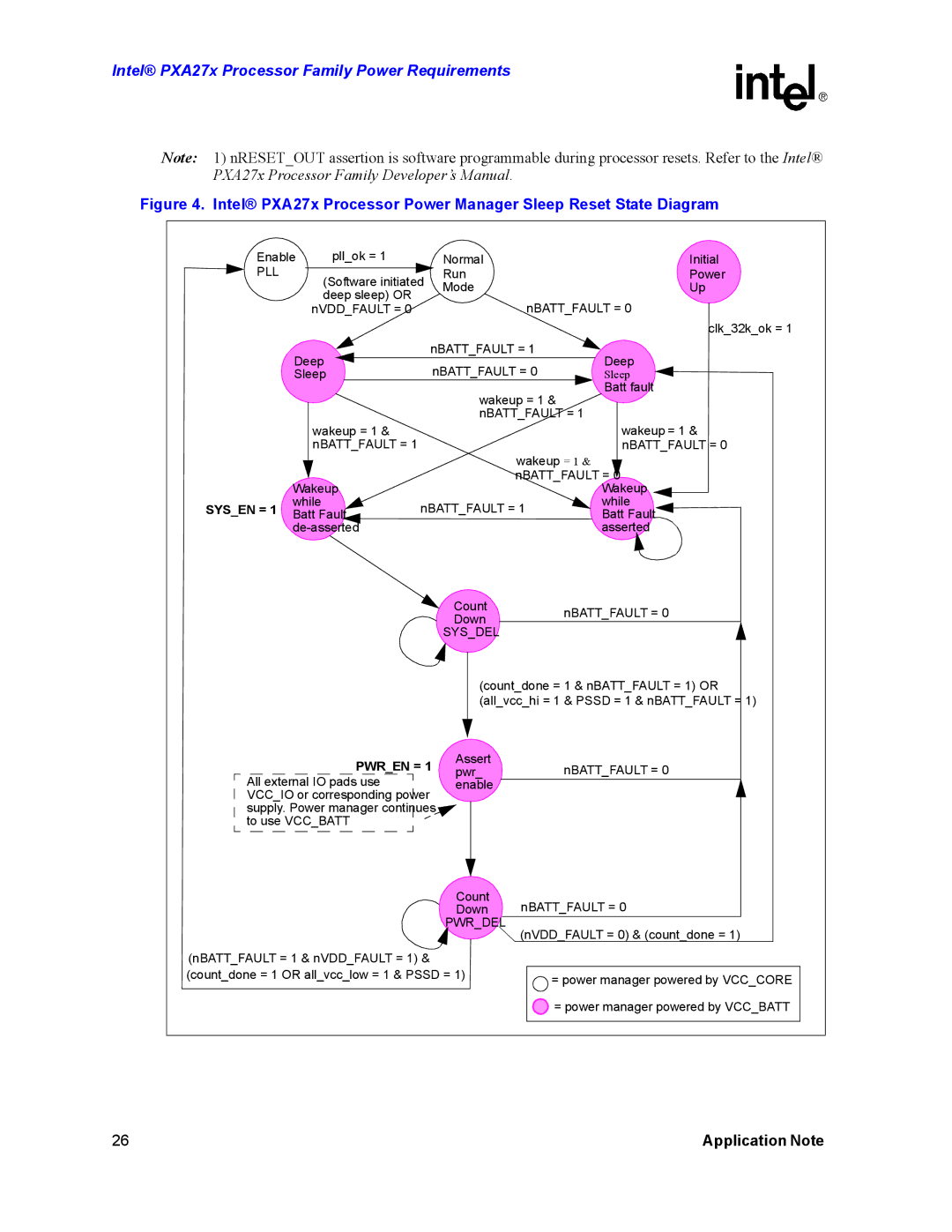

Note: 1) nRESET_OUT assertion is software programmable during processor resets. Refer to the Intel® PXA27x Processor Family Developer’s Manual.

Figure 4. Intel® PXA27x Processor Power Manager Sleep Reset State Diagram

Enable | pll_ok = 1 |

| Normal | Initial |

PLL | (Software initiated | Run | Power | |

| Mode | Up | ||

| deep sleep) OR | |||

|

| nBATT_FAULT = 0 | ||

| nVDD_FAULT = 0 |

| ||

clk_32k_ok = 1

| Deep |

| nBATT_FAULT = 1 | Deep | ||||||

|

| nBATT_FAULT = 0 |

| |||||||

| Sleep |

| Sleep | |||||||

|

|

|

|

| wakeup = 1 & | Batt fault | ||||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| nBATT_FAULT = 1 |

|

|

|

| |

|

| wakeup = 1 & |

|

|

| wakeup = 1 & | ||||

|

| nBATT_FAULT = 1 |

|

|

| nBATT_FAULT = 0 | ||||

|

|

|

|

| wakeup = 1 & |

|

|

|

| |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| nBATT_FAULT = 0 | |||||

| Wakeup |

|

| Wakeup |

|

| ||||

SYS_EN = 1 | while | nBATT_FAULT = 1 | while | |||||||

Batt Fault | Batt Fault | |||||||||

|

|

| asserted | |||||||

Count | nBATT_FAULT = 0 | |

Down |

| |

SYS_DEL |

| |

(count_done = 1 & nBATT_FAULT = 1) OR

(all_vcc_hi = 1 & PSSD = 1 & nBATT_FAULT = 1)

|

|

|

|

|

|

|

|

|

| PWR_EN | = 1 | Assert | nBATT_FAULT = 0 | |||||||

|

|

|

|

|

|

|

|

|

| pwr_ | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

All external IO pads use |

|

| ||||||||||||||||||

|

| enable |

| |||||||||||||||||

| ||||||||||||||||||||

|

|

| ||||||||||||||||||

VCC_IO or corresponding power |

|

|

| |||||||||||||||||

supply. Power manager continu |

| es |

|

|

| |||||||||||||||

|

|

| ||||||||||||||||||

|

|

|

| |||||||||||||||||

to use VCC_BATT |

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Count | nBATT_FAULT = 0 |

| ||||

Down |

| |||||

PWR_DEL |

| (nVDD_FAULT = 0) & (count_done = 1) | ||||

|

| |||||

(nBATT_FAULT = 1 & nVDD_FAULT = 1) & |

|

|

|

|

| |

(count_done = 1 OR all_vcc_low = 1 & PSSD = 1) |

| = power manager powered by VCC_CORE |

| |||

|

|

|

| |||

|

|

| = power manager powered by VCC_BATT |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

26 | Application Note |