MS/s, 12-bit, 16-ch High- Speed Multifunction Card

PCI-1712/1712L Quick Start Unpacking

Device Installation

Page

Contents

Appendix D. Register Structure and Format

Calibration

100

Figures

Auto A/D Calibration Dialog Box

Corresponding Full Scale values for various Input

I/O Connector Signal Description Part

Table D-1PCI-1712/1712L register format Part Table D-2

Table D-3

101

100

102

Page

Introduction

Features

Plug-and-Play Function

PCI-Bus Mastering Data Transfer

On-board Fifo Memory

Automatic Channel/Gain/SD*/BU* Scanning

On-board Programmable Multifunction Counter/Timer

Installation Guide

Continuous Analog Output

Installation Flow Chart

Wiring Cable

Accessories

Wiring Boards

Chapter

Unpacking

Installation

Setup Screen of Advantech Automation Software

Driver Installation

Different options for Driver Setup

Hardware Installation

Chapter

Device name listed on the Device Manager

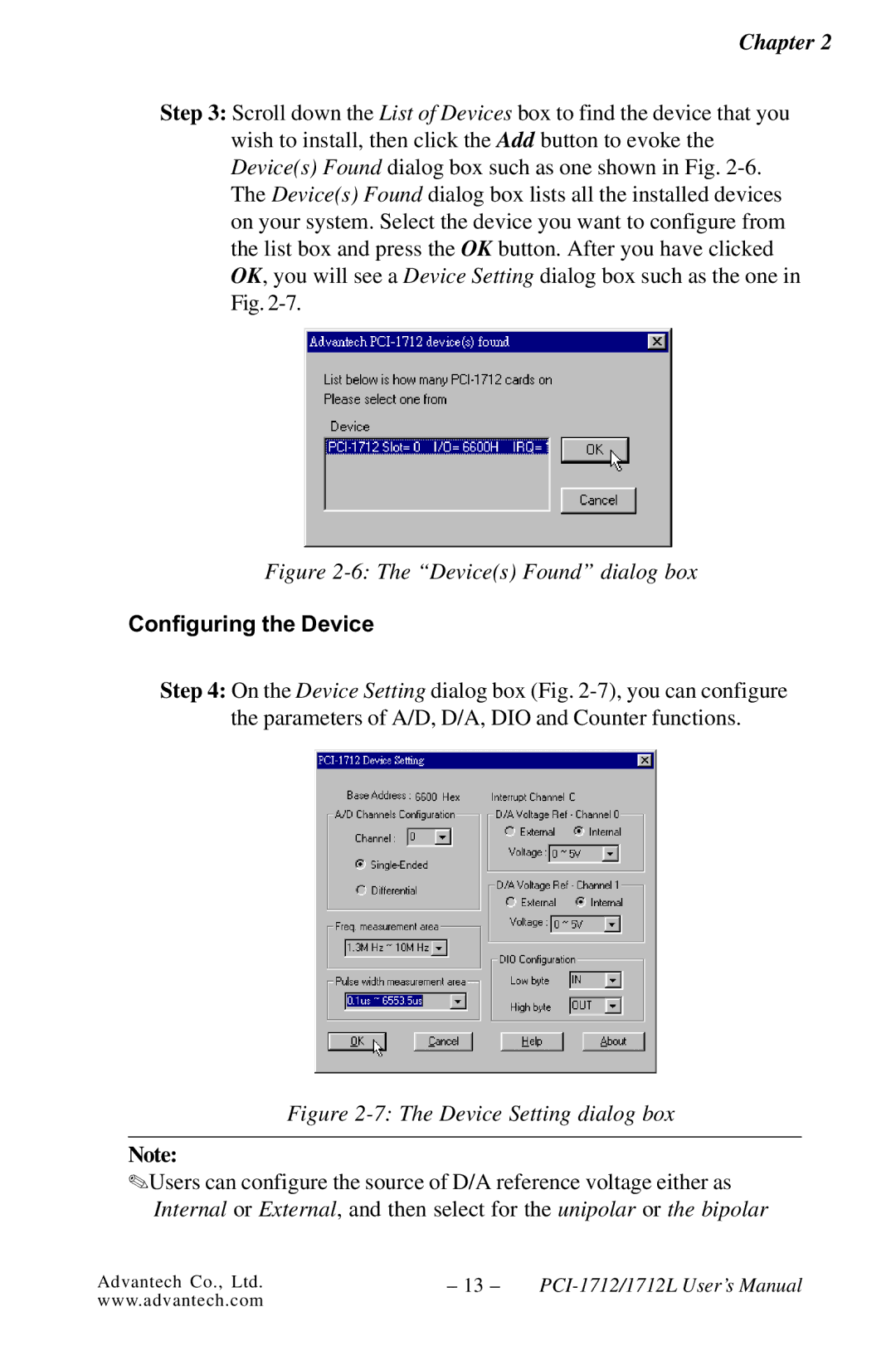

Setting Up the Device

Device Setup & Configuration

Devices Found dialog box

Configuring the Device

For bipolar

For unipolar

Testing Analog Input Function

Device Testing

Testing Digital Input Function

Testing Analog Output Function PCI-1712 only

Testing Counter Function

Testing Digital Output Function

14 Digital output tab on the Device Test dialog box

I/O Connector

Signal Connections

Overview

Pin Assignment

I/O connector pin assignments for the PCI-1712/1712L

I/O Connector Signal Description Part

Connector Signal Description

Signal Name Reference Direction Description

Counter 0 Gate Input. This pin is for

Single-ended Channel Connections

Analog Input Connections

Differential Channel Connections

Chapter

Differential input channel connection floating signal Source

Analog output connections

Analog Output Connections

Field Wiring Considerations

Programming Choices

Software Overview

DLL Driver

Register-level Programming

Programming Tools

DLL Driver Programming Roadmap

Programming with DLL Driver Function Library

Troubleshooting DLL Driver Error

Chapter

Principles of Operation

Analog Input Features

Analog Input Ranges and Gains

Gains and Analog Input Range

Analog Input Acquisition Modes

Post-Trigger Acquisition Mode

About-Trigger Acquisition Mode

Sample Clock Sources

Pre-Trigger Acquisition Mode

Trigger Sources

PCI-1712/1712L Sample Clock Source

Analog Input Data Format

Analog Input Data Format

Analog Output Ranges

Analog Output Features

Analog Output Operation Modes

Output Clock Sources

Trigger Sources

Analog Output Data Format

Digital I/O Features

Analog Output Data Format

Clock sources

Counter/Timer Features

Gate Types and Sources

Counter/timer operation modes

Chapter

Chapter

Frequency measurement

Chapter

Chapter

Pulse width measurement

Internal, and gate use for pulse

Show the duty ratio of positive

VR Assignment

Calibration

A/D Calibration

D/A Calibration

Selecting the device you want to calibrate

Calibration Utility

Auto A/D Calibration Dialog Box

Channel Auto-Calibration

A/D Calibration Procedure

A/D Calibration is finished

Range Selection in D/A Calibration

11 Calibrating D/A Channel

13 Selecting Input Rage in Manual A/D Calibration panel

Channel Manual-Calibration

14 Adjusting registers

15 & -16 Selecting D/A Range Choosing Output Voltage

17 Adjusting registers

Chapter

Analog Input

Specification

Digital Input /Output

Analog Output PCI-1712 only

General

Counter/Timer

Appendix a

Block Diagram

Block Diagram

Appendix B

Board Layout

Screw-terminal Board

Figure C-2 CN2 pin assignments for the PCLD-8712

Pin Assignment

Single-ended Connections

Differential Connections

I/O Port Address Map

Register Structure and Format

Table D-1 PCI-1712/1712L register format Part

Appendix D

Base PCI-1712/1712L Register Format Address

Channel data for continuous output operation mode 30 W

Channel and A/D data Read Base +

A/D Single Value Acquisition Write BASE+0

Data of A/D Conversion

CH2 to CH0 Channel Number

Table D-3 Register for A/D channel range setting

A/D Channel Range Setting Write BASE+2

Single-ended or Differential

Bipolar or Unipolar

Table D-4 Gain Codes for the PCI-1712/1712L

MUX Control Write BASE+4

Table D-5 Register for multiplexer control

Start Scan Channel Number

Appendix D

A/D Control/Status Register Write/Read BASE+6

Analog input acquisition mode register

Table D-6 Register for A/D control/status

Trigger source control register

Sample clock source select register

Trigger edge control register

Analog I/O calibration bit

Aitrgf Analog input trigger flag

Clear interrupt and Fifo Write BASE+8

Table D-8 Register for clear interrupt and Fifo

Clear A/D Fifo

Interrupt flag

Interrupt and Fifo status Read BASE+8

Fifo empty flag

Fifo half-full flag

10 D/A control/status register Write/Read BASE+A

Channel 1 unipolar or bipolar output

Table D-11 Analog output operation mode

Clock source select register

Aotrgf Analog output trigger flag

Table D-12 Register for D/A channel 0/1 data

11 D/A Channel 0/1 Data Write BASE+C/E

Data

Table D-13 Register for 82C54 counter chip

12 82C54 Counter Chip 0 Write/Read BASE+10 to

Table D-14 Register for 82C54 counter chip

13 82C54 counter chip 1 Write/Read BASE+18 to 1E

Table D-16 Table of Cn1 to Cn0 register

Cn1 to Cn0 Counter clock source control register n = 0,1,2

CQn Counter clock set register n = 0,1,2

CPn Counter clock edge control register n = 0,1,2

Gn1 to Gn0 Counter gate source control register n = 0,1,2

Table D-17 Table of Gn1 to Gn0 register

GPn Counter gate polarity control register n = 0,1,2

GRn Pulse width measurement reset register n = 0,1,2

GQn Counter gate set register n = 0,1,2

GATEn Gate status n = 0,1,2

GATESn Pulse width measurement status bit n = 0,1,2

Digital I/O registers Write/Read BASE+28

CLKSEL1 & 0 Counter internal clock select register

DO15 to DO0 Digital output data register

Calibration command registers Write BASE+2C

Digital I/O configuration registers Write/Read BASE+2A

DIOC1 to DIOC0 Digital I/O configuration register

DI15 to DI0 Digital input data register

Table D-23 Calibration command

CM3 to CM0 Calibration command

D7 to D0 Calibration data

DA11 to DA0 D/A data

Table D-24 Register for D/A channel data