|

|

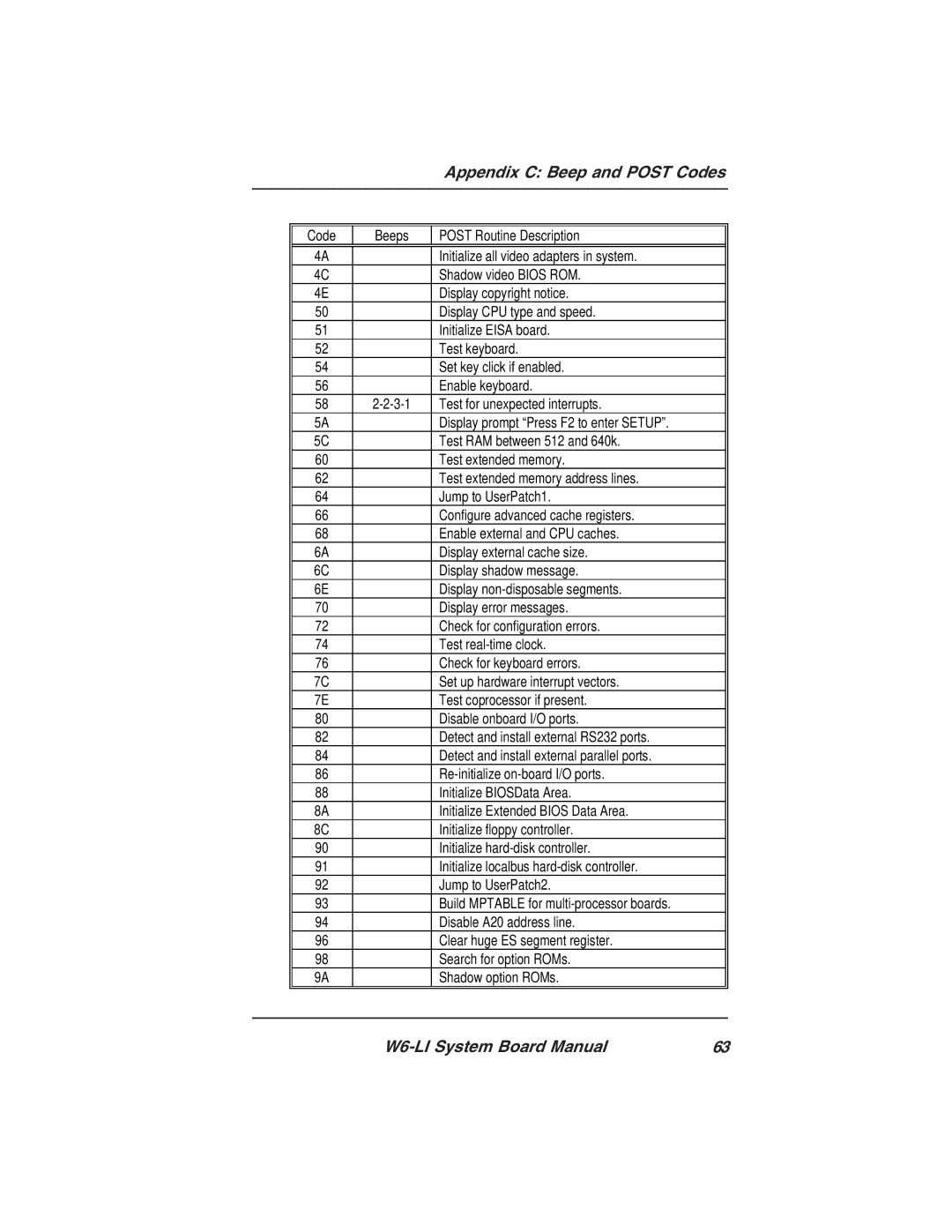

| Appendix C: Beep and POST Codes |

|

|

|

|

|

|

|

|

| Code | Beeps | POST Routine Description |

|

|

|

|

| 4A |

| Initialize all video adapters in system. |

| 4C |

| Shadow video BIOS ROM. |

| 4E |

| Display copyright notice. |

| 50 |

| Display CPU type and speed. |

| 51 |

| Initialize EISA board. |

| 52 |

| Test keyboard. |

| 54 |

| Set key click if enabled. |

| 56 |

| Enable keyboard. |

| 58 | Test for unexpected interrupts. | |

| 5A |

| Display prompt “Press F2 to enter SETUP”. |

| 5C |

| Test RAM between 512 and 640k. |

| 60 |

| Test extended memory. |

| 62 |

| Test extended memory address lines. |

| 64 |

| Jump to UserPatch1. |

| 66 |

| Configure advanced cache registers. |

| 68 |

| Enable external and CPU caches. |

| 6A |

| Display external cache size. |

| 6C |

| Display shadow message. |

| 6E |

| Display |

| 70 |

| Display error messages. |

| 72 |

| Check for configuration errors. |

| 74 |

| Test |

| 76 |

| Check for keyboard errors. |

| 7C |

| Set up hardware interrupt vectors. |

| 7E |

| Test coprocessor if present. |

| 80 |

| Disable onboard I/O ports. |

| 82 |

| Detect and install external RS232 ports. |

| 84 |

| Detect and install external parallel ports. |

| 86 |

| |

| 88 |

| Initialize BIOSData Area. |

| 8A |

| Initialize Extended BIOS Data Area. |

| 8C |

| Initialize floppy controller. |

| 90 |

| Initialize |

| 91 |

| Initialize localbus |

| 92 |

| Jump to UserPatch2. |

| 93 |

| Build MPTABLE for |

| 94 |

| Disable A20 address line. |

| 96 |

| Clear huge ES segment register. |

| 98 |

| Search for option ROMs. |

| 9A |

| Shadow option ROMs. |

|

|

|

|

63 |