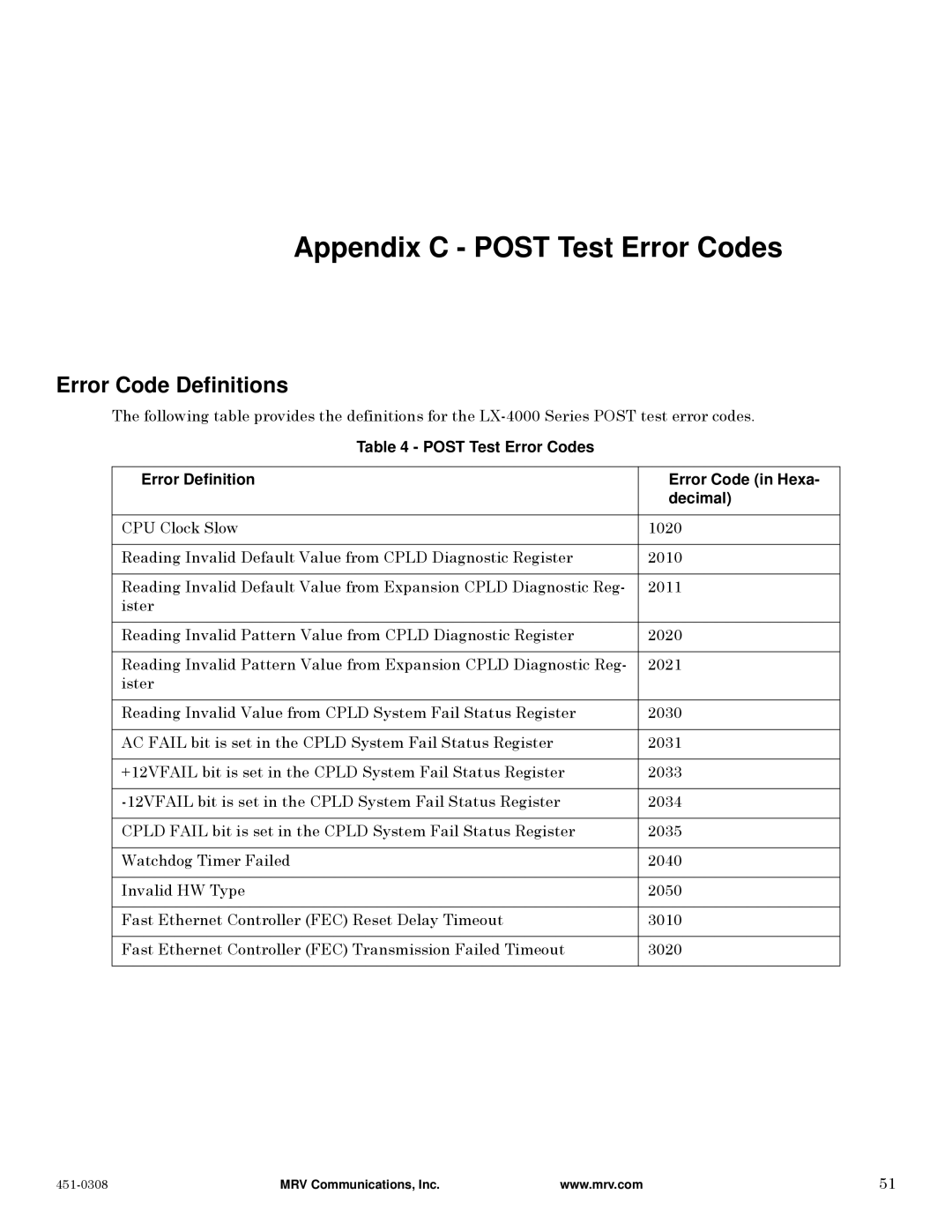

Appendix C - POST Test Error Codes

Error Code Definitions

The following table provides the definitions for the

Table 4 - POST Test Error Codes

Error Definition | Error Code (in Hexa- |

| decimal) |

|

|

CPU Clock Slow | 1020 |

|

|

Reading Invalid Default Value from CPLD Diagnostic Register | 2010 |

|

|

Reading Invalid Default Value from Expansion CPLD Diagnostic Reg- | 2011 |

ister |

|

|

|

Reading Invalid Pattern Value from CPLD Diagnostic Register | 2020 |

|

|

Reading Invalid Pattern Value from Expansion CPLD Diagnostic Reg- | 2021 |

ister |

|

|

|

Reading Invalid Value from CPLD System Fail Status Register | 2030 |

|

|

AC FAIL bit is set in the CPLD System Fail Status Register | 2031 |

|

|

+12VFAIL bit is set in the CPLD System Fail Status Register | 2033 |

|

|

2034 | |

|

|

CPLD FAIL bit is set in the CPLD System Fail Status Register | 2035 |

|

|

Watchdog Timer Failed | 2040 |

|

|

Invalid HW Type | 2050 |

|

|

Fast Ethernet Controller (FEC) Reset Delay Timeout | 3010 |

|

|

Fast Ethernet Controller (FEC) Transmission Failed Timeout | 3020 |

|

|

MRV Communications, Inc. | www.mrv.com | 51 |