Unbuffered DIMM

datasheet

Rev. 1.0

DDR3L SDRAM

11.3 AC and DC Logic Input Levels for Differential Signals

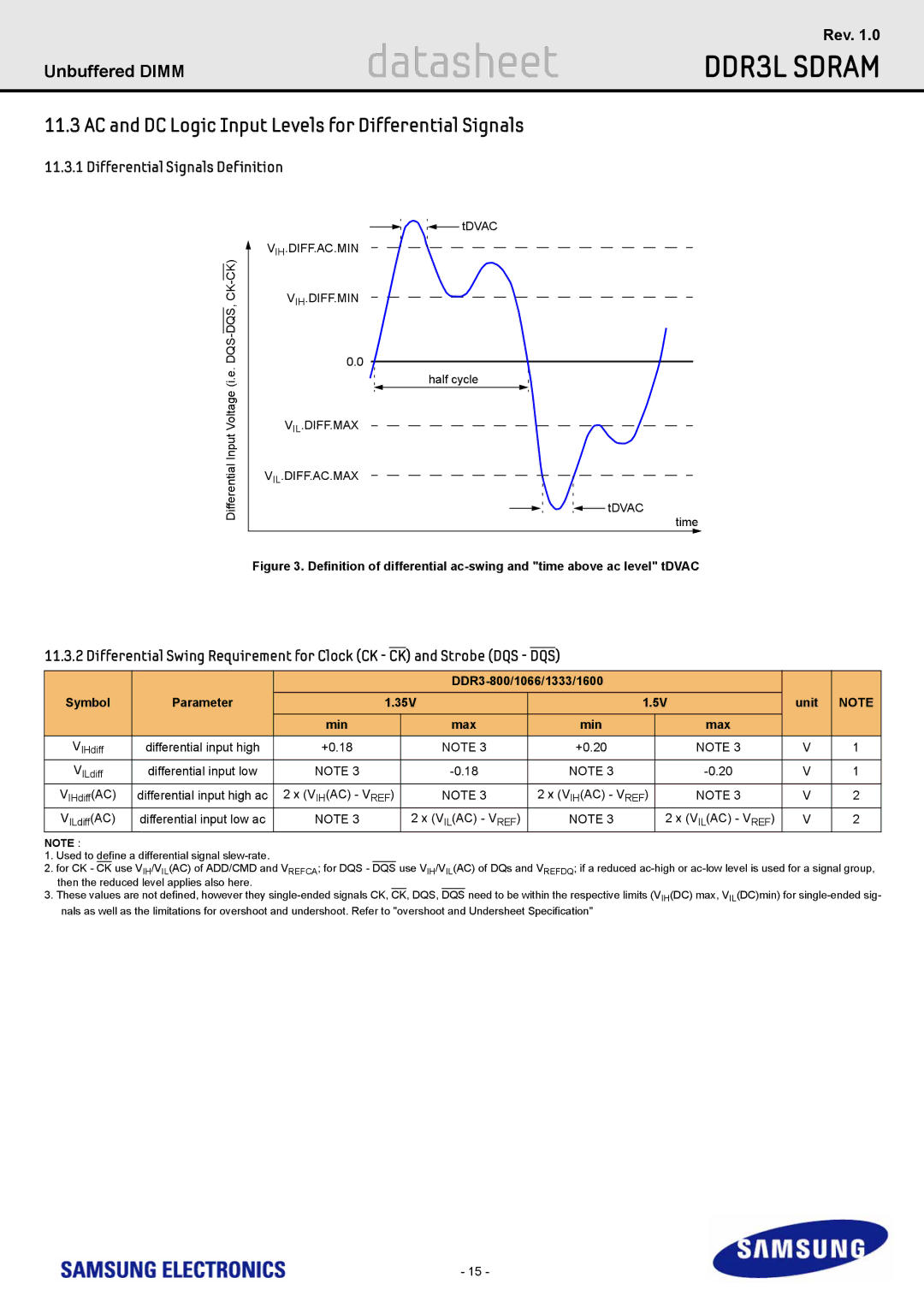

11.3.1 Differential Signals Definition

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tDVAC | ||||||||||||||||||||||||||||

|

| VIH.DIFF.AC.MIN |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| VIH.DIFF.MIN | ||||||||||||||||||||||||||||||||||||||||||||

|

| |||||||||||||||||||||||||||||||||||||||||||||

|

| 0.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

(i.e. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| half cycle | |||||||||||||||||||||||||||||||||||

Voltage |

| VIL.DIFF.MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Differential |

| VIL.DIFF.AC.MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tDVAC | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| time | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 3. Definition of differential ac-swing and "time above ac level" tDVAC

11.3.2 Differential Swing Requirement for Clock (CK - CK) and Strobe (DQS - DQS)

|

|

|

|

|

| ||

Symbol | Parameter | 1.35V | 1.5V | unit | NOTE | ||

|

| min | max | min | max |

|

|

VIHdiff | differential input high | +0.18 | NOTE 3 | +0.20 | NOTE 3 | V | 1 |

VILdiff | differential input low | NOTE 3 | NOTE 3 | V | 1 | ||

VIHdiff(AC) | differential input high ac | 2 x (VIH(AC) - VREF) | NOTE 3 | 2 x (VIH(AC) - VREF) | NOTE 3 | V | 2 |

VILdiff(AC) | differential input low ac | NOTE 3 | 2 x (VIL(AC) - VREF) | NOTE 3 | 2 x (VIL(AC) - VREF) | V | 2 |

NOTE :

1.Used to define a differential signal

2.for CK - CK use VIH/VIL(AC) of ADD/CMD and VREFCA; for DQS - DQS use VIH/VIL(AC) of DQs and VREFDQ; if a reduced

3.These values are not defined, however they

nals as well as the limitations for overshoot and undershoot. Refer to "overshoot and Undersheet Specification"

- 15 -