Unbuffered DIMM

datasheet

Rev. 1.0

DDR3L SDRAM

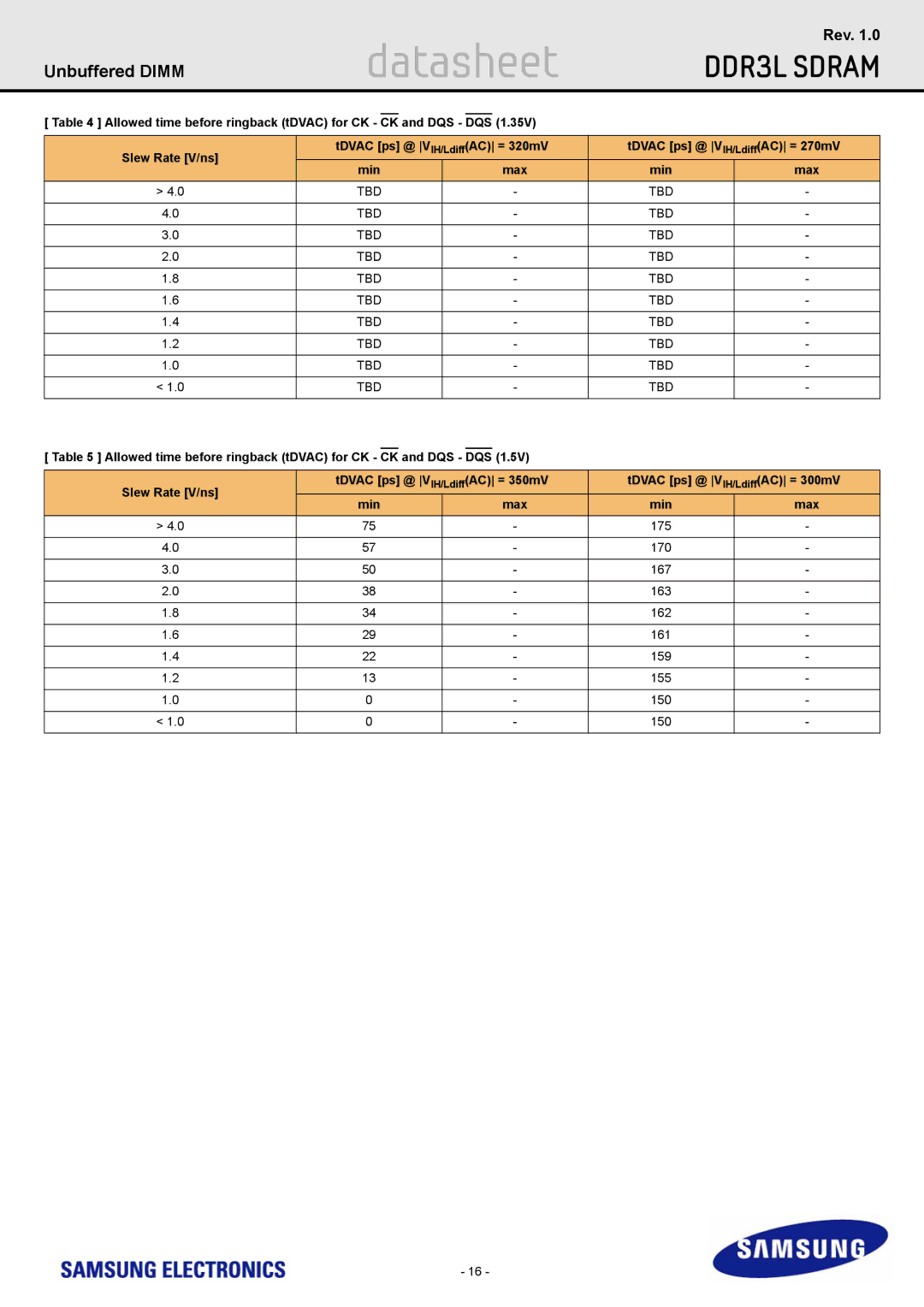

[ Table 4 ] Allowed time before ringback (tDVAC) for CK - CK and DQS - DQS (1.35V)

Slew Rate [V/ns] | tDVAC [ps] @ VIH/Ldiff(AC) = 320mV | tDVAC [ps] @ VIH/Ldiff(AC) = 270mV | |||

min | max | min | max | ||

| |||||

> 4.0 | TBD | - | TBD | - | |

|

|

|

|

| |

4.0 | TBD | - | TBD | - | |

|

|

|

|

| |

3.0 | TBD | - | TBD | - | |

|

|

|

|

| |

2.0 | TBD | - | TBD | - | |

|

|

|

|

| |

1.8 | TBD | - | TBD | - | |

|

|

|

|

| |

1.6 | TBD | - | TBD | - | |

|

|

|

|

| |

1.4 | TBD | - | TBD | - | |

|

|

|

|

| |

1.2 | TBD | - | TBD | - | |

|

|

|

|

| |

1.0 | TBD | - | TBD | - | |

|

|

|

|

| |

< 1.0 | TBD | - | TBD | - | |

|

|

|

|

| |

[ Table 5 ] Allowed time before ringback (tDVAC) for CK - CK and DQS - DQS (1.5V)

Slew Rate [V/ns] | tDVAC [ps] @ VIH/Ldiff(AC) = 350mV | tDVAC [ps] @ VIH/Ldiff(AC) = 300mV | |||

min | max | min | max | ||

| |||||

> 4.0 | 75 | - | 175 | - | |

|

|

|

|

| |

4.0 | 57 | - | 170 | - | |

|

|

|

|

| |

3.0 | 50 | - | 167 | - | |

|

|

|

|

| |

2.0 | 38 | - | 163 | - | |

|

|

|

|

| |

1.8 | 34 | - | 162 | - | |

|

|

|

|

| |

1.6 | 29 | - | 161 | - | |

|

|

|

|

| |

1.4 | 22 | - | 159 | - | |

|

|

|

|

| |

1.2 | 13 | - | 155 | - | |

|

|

|

|

| |

1.0 | 0 | - | 150 | - | |

|

|

|

|

| |

< 1.0 | 0 | - | 150 | - | |

|

|

|

|

| |

- 16 -