Unbuffered DIMM

datasheet

Rev. 1.0

DDR3L SDRAM

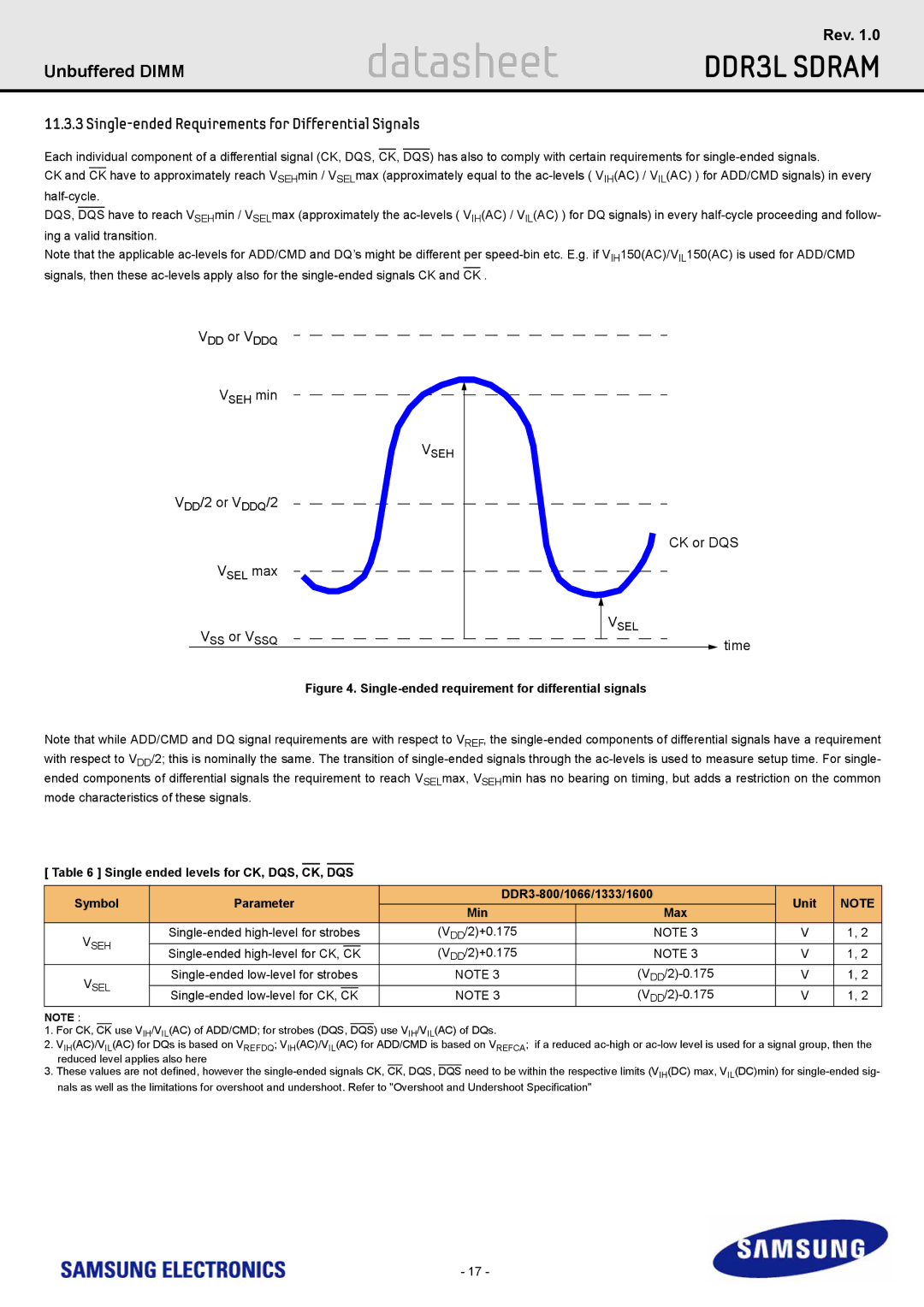

11.3.3 Single-ended Requirements for Differential Signals

Each individual component of a differential signal (CK, DQS, CK, DQS) has also to comply with certain requirements for

CK and CK have to approximately reach VSEHmin / VSELmax (approximately equal to the

DQS, DQS have to reach VSEHmin / VSELmax (approximately the

Note that the applicable

signals, then these

VDD or VDDQ

VSEH min

VSEH

VDD/2 or VDDQ/2

VSEL max

VSS or VSSQ

CK or DQS

VSEL

time

time

Figure 4. Single-ended requirement for differential signals

Note that while ADD/CMD and DQ signal requirements are with respect to VREF, the

[ Table 6 ] Single ended levels for CK, DQS, CK, DQS

Symbol | Parameter |

|

| Unit | NOTE | ||||

| Min | Max | |||||||

|

|

|

|

|

|

|

| ||

VSEH |

| (VDD/2)+0.175 | NOTE 3 | V | 1, 2 | ||||

|

|

|

|

| (VDD/2)+0.175 |

|

|

| |

| NOTE 3 | V | 1, 2 | ||||||

|

| ||||||||

VSEL |

| NOTE 3 | V | 1, 2 | |||||

|

|

|

|

|

|

|

| ||

| NOTE 3 | V | 1, 2 | ||||||

|

| ||||||||

NOTE :

1.For CK, CK use VIH/VIL(AC) of ADD/CMD; for strobes (DQS, DQS) use VIH/VIL(AC) of DQs.

2.VIH(AC)/VIL(AC) for DQs is based on VREFDQ; VIH(AC)/VIL(AC) for ADD/CMD is based on VREFCA; if a reduced

3.These values are not defined, however the

- 17 -