Unbuffered DIMM

datasheet

Rev. 1.0

DDR3L SDRAM

11.2 VREF Tolerances

The

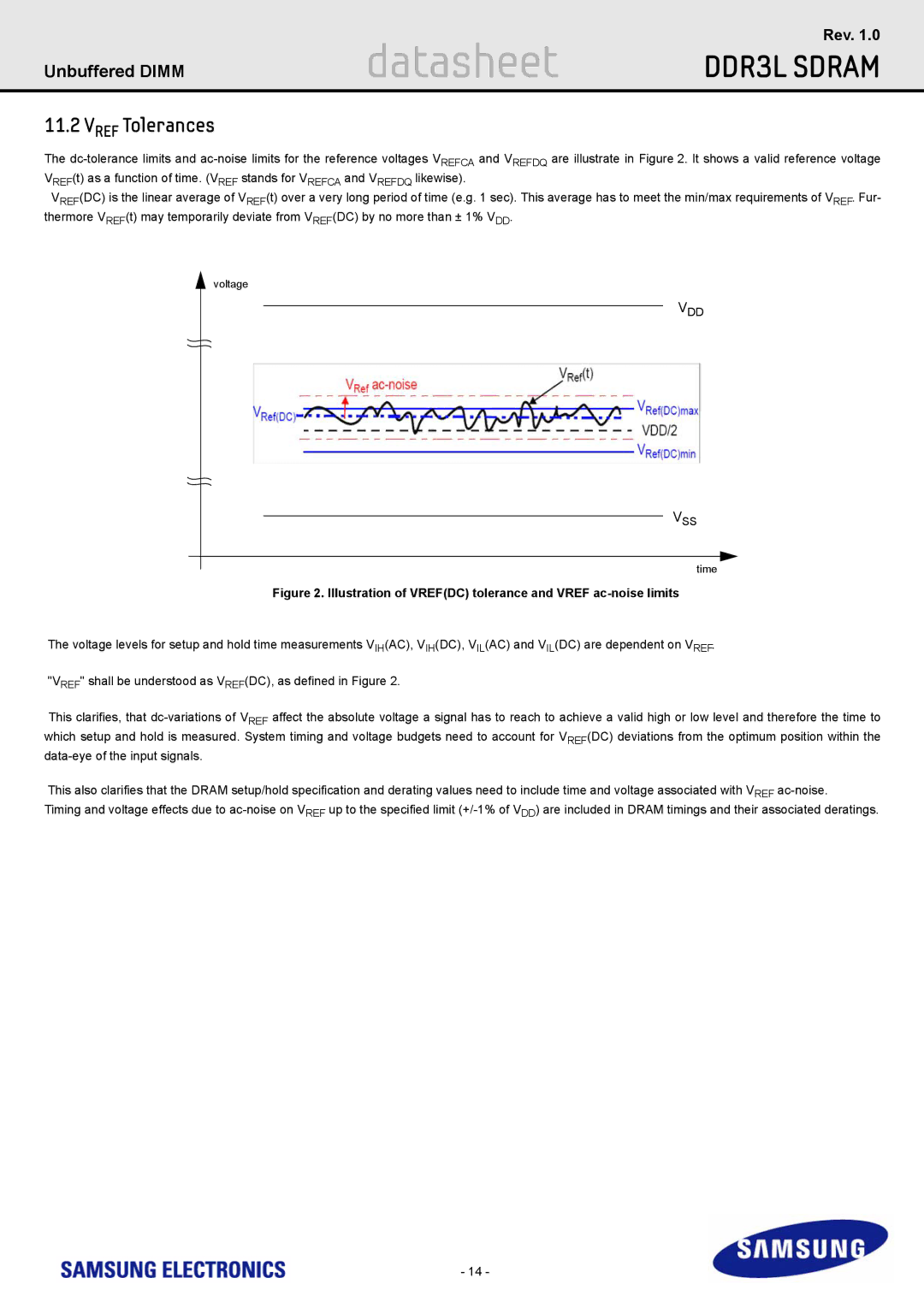

VREF(DC) is the linear average of VREF(t) over a very long period of time (e.g. 1 sec). This average has to meet the min/max requirements of VREF. Fur- thermore VREF(t) may temporarily deviate from VREF(DC) by no more than ± 1% VDD.

voltage |

VDD |

VSS |

time |

Figure 2. Illustration of VREF(DC) tolerance and VREF ac-noise limits

The voltage levels for setup and hold time measurements VIH(AC), VIH(DC), VIL(AC) and VIL(DC) are dependent on VREF.

"VREF" shall be understood as VREF(DC), as defined in Figure 2.

This clarifies, that

This also clarifies that the DRAM setup/hold specification and derating values need to include time and voltage associated with VREF

Timing and voltage effects due to

- 14 -