Unbuffered DIMM

datasheet

Rev. 1.0

DDR3L SDRAM

11.4 Slew Rate Definition for Single Ended Input Signals

See "Address / Command Setup, Hold and Derating" for

11.5 Slew rate definition for Differential Input Signals

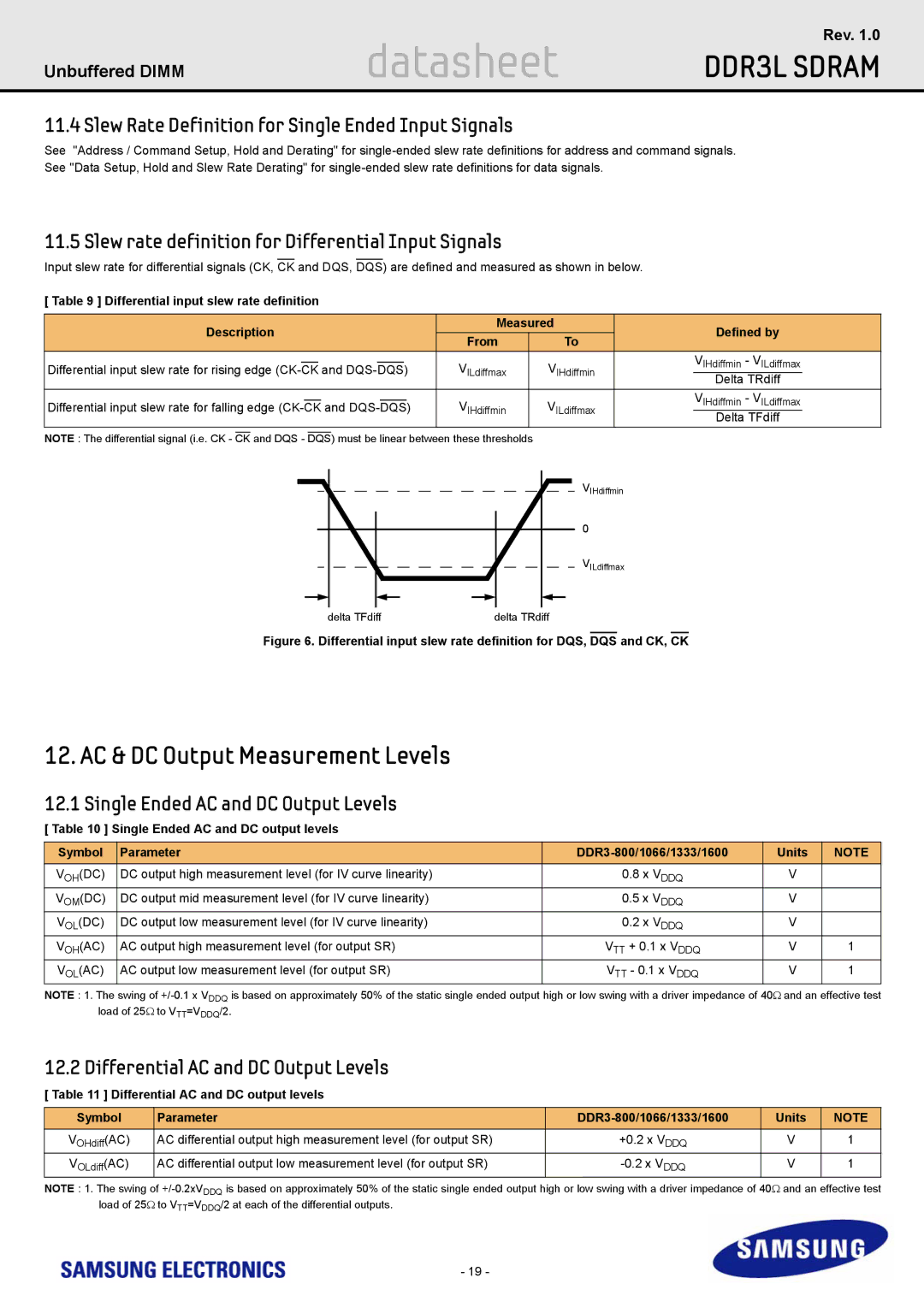

Input slew rate for differential signals (CK, CK and DQS, DQS) are defined and measured as shown in below.

[ Table 9 ] Differential input slew rate definition

Description | Measured |

| Defined by | |||||||||||||||

From |

| To |

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| VILdiffmax |

| VIHdiffmin |

| VIHdiffmin - VILdiffmax |

|

Differential input slew rate for rising edge |

| |||||||||||||||||

|

| Delta TRdiff | ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| VIHdiffmin |

| VILdiffmax |

| VIHdiffmin - VILdiffmax |

|

Differential input slew rate for falling edge |

| |||||||||||||||||

|

| Delta TFdiff | ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

NOTE : The differential signal (i.e. CK - |

| and DQS - |

|

|

| must be linear between these thresholds |

|

|

|

| ||||||||

CK | DQS) |

|

|

|

| |||||||||||||

| VIHdiffmin |

| 0 |

| VILdiffmax |

delta TFdiff | delta TRdiff |

Figure 6. Differential input slew rate definition for DQS, DQS and CK, CK

12. AC & DC Output Measurement Levels

12.1 Single Ended AC and DC Output Levels

[ Table 10 ] Single Ended AC and DC output levels

Symbol | Parameter | Units | NOTE | |

VOH(DC) | DC output high measurement level (for IV curve linearity) | 0.8 x VDDQ | V |

|

VOM(DC) | DC output mid measurement level (for IV curve linearity) | 0.5 x VDDQ | V |

|

VOL(DC) | DC output low measurement level (for IV curve linearity) | 0.2 x VDDQ | V |

|

VOH(AC) | AC output high measurement level (for output SR) | VTT + 0.1 x VDDQ | V | 1 |

VOL(AC) | AC output low measurement level (for output SR) | VTT - 0.1 x VDDQ | V | 1 |

NOTE : 1. The swing of

12.2 Differential AC and DC Output Levels

[ Table 11 ] Differential AC and DC output levels

Symbol | Parameter | Units | NOTE | |

VOHdiff(AC) | AC differential output high measurement level (for output SR) | +0.2 x VDDQ | V | 1 |

VOLdiff(AC) | AC differential output low measurement level (for output SR) | V | 1 |

NOTE : 1. The swing of

- 19 -