Unbuffered DIMM

datasheet

Rev. 1.0

DDR3L SDRAM

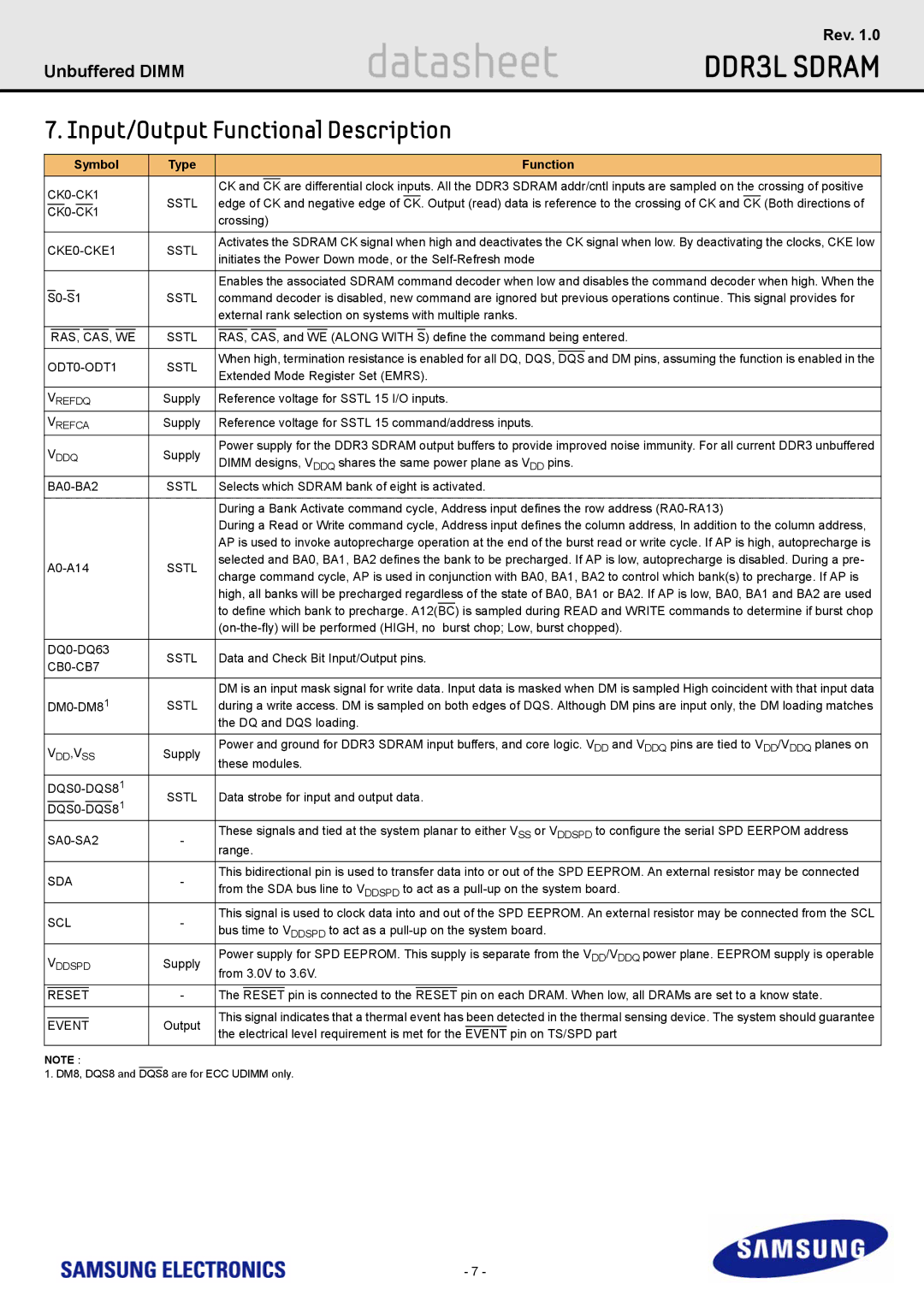

7. Input/Output Functional Description

|

|

|

| Symbol |

| Type |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Function | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| CK and |

|

| are differential clock inputs. All the DDR3 SDRAM addr/cntl inputs are sampled on the crossing of positive | |||||||||||||||||||

|

|

|

| CK | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

| SSTL |

| edge of CK and negative edge of CK. Output (read) data is reference to the crossing of CK and CK (Both directions of | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||

|

|

|

| crossing) | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

| SSTL |

| Activates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low | ||||||||||||||||||||||||||||||

|

|

| initiates the Power Down mode, or the | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Enables the associated SDRAM command decoder when low and disables the command decoder when high. When the | ||||||||||||||||||||||

|

| SSTL |

| command decoder is disabled, new command are ignored but previous operations continue. This signal provides for | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| external rank selection on systems with multiple ranks. | ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

| SSTL |

|

|

|

|

|

| and |

| (ALONG WITH |

|

|

|

|

|

|

|

|

|

|

| ||||

| RAS, | CAS, | WE | RAS, | CAS, | WE | S) define the command being entered. | ||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| When high, termination resistance is enabled for all DQ, DQS, |

| and DM pins, assuming the function is enabled in the | ||||||||||||||||||||

|

|

| SSTL |

| DQS | ||||||||||||||||||||||||||||||

|

|

| Extended Mode Register Set (EMRS). | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

| |||||||||||||||||||||||||||||||

| VREFDQ |

| Supply | Reference voltage for SSTL 15 I/O inputs. | |||||||||||||||||||||||||||||||

| VREFCA |

| Supply | Reference voltage for SSTL 15 command/address inputs. | |||||||||||||||||||||||||||||||

| VDDQ |

| Supply |

| Power supply for the DDR3 SDRAM output buffers to provide improved noise immunity. For all current DDR3 unbuffered | ||||||||||||||||||||||||||||||

|

|

| DIMM designs, VDDQ shares the same power plane as VDD pins. | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

| SSTL | Selects which SDRAM bank of eight is activated. | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| During a Bank Activate command cycle, Address input defines the row address | ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| During a Read or Write command cycle, Address input defines the column address, In addition to the column address, | ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| AP is used to invoke autoprecharge operation at the end of the burst read or write cycle. If AP is high, autoprecharge is | ||||||||||||||||||||||

|

| SSTL |

| selected and BA0, BA1, BA2 defines the bank to be precharged. If AP is low, autoprecharge is disabled. During a pre- | |||||||||||||||||||||||||||||||

|

|

| charge command cycle, AP is used in conjunction with BA0, BA1, BA2 to control which bank(s) to precharge. If AP is | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| high, all banks will be precharged regardless of the state of BA0, BA1 or BA2. If AP is low, BA0, BA1 and BA2 are used | ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| is sampled during READ and WRITE commands to determine if burst chop | ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| to define which bank to precharge. A12(BC) |

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| SSTL | Data and Check Bit Input/Output pins. | ||||||||||||||||||||||||||||||||

|

|

| |||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| DM is an input mask signal for write data. Input data is masked when DM is sampled High coincident with that input data | ||||||||||||||||||||||

|

| SSTL |

| during a write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| the DQ and DQS loading. | ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

| VDD,VSS |

| Supply |

| Power and ground for DDR3 SDRAM input buffers, and core logic. VDD and VDDQ pins are tied to VDD/VDDQ planes on | ||||||||||||||||||||||||||||||

|

|

| these modules. | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| SSTL | Data strobe for input and output data. | ||||||||||||||||||||||||||||||||

|

|

|

|

| - |

|

| 1 |

| ||||||||||||||||||||||||||

| DQS0 | DQS8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

| - |

| These signals and tied at the system planar to either VSS or VDDSPD to configure the serial SPD EERPOM address | |||||||||||||||||||||||||||||||

|

|

| range. | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

| SDA |

| - |

| This bidirectional pin is used to transfer data into or out of the SPD EEPROM. An external resistor may be connected | ||||||||||||||||||||||||||||||

|

|

| from the SDA bus line to VDDSPD to act as a | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

| SCL |

| - |

| This signal is used to clock data into and out of the SPD EEPROM. An external resistor may be connected from the SCL | ||||||||||||||||||||||||||||||

|

|

| bus time to VDDSPD to act as a | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

| VDDSPD |

| Supply |

| Power supply for SPD EEPROM. This supply is separate from the VDD/VDDQ power plane. EEPROM supply is operable | ||||||||||||||||||||||||||||||

|

|

| from 3.0V to 3.6V. | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||

|

|

|

|

|

|

|

| - |

| The |

|

|

|

|

|

| pin is connected to the |

|

|

|

|

| pin on each DRAM. When low, all DRAMs are set to a know state. | ||||||||||||

| RESET |

| RESET | RESET | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| This signal indicates that a thermal event has been detected in the thermal sensing device. The system should guarantee | ||||||||||||||||||||||

| EVENT |

| Output |

| |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

| the electrical level requirement is met for the EVENT pin on TS/SPD part | |||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE :

1. DM8, DQS8 and DQS8 are for ECC UDIMM only.

- 7 -