|

|

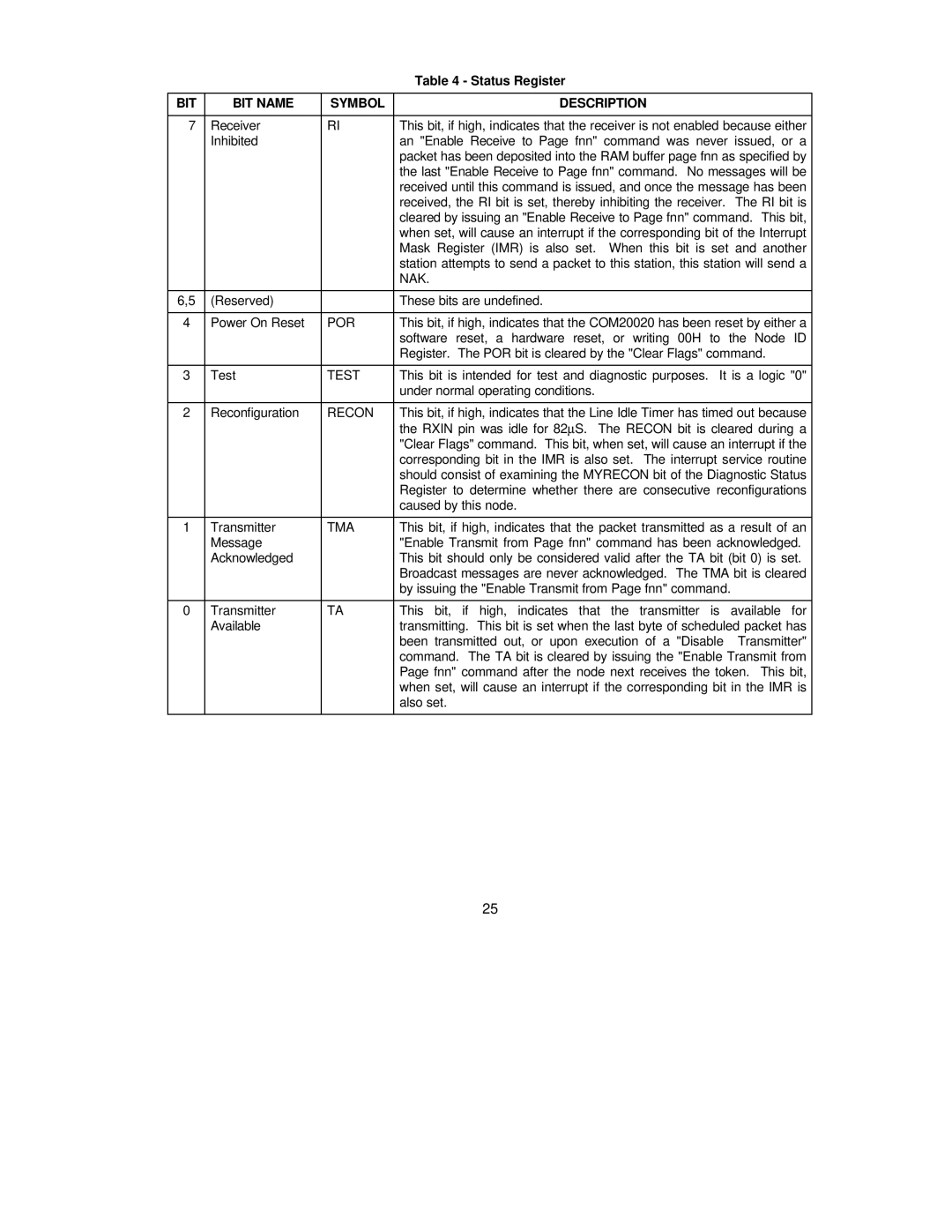

| Table 4 - Status Register |

BIT | BIT NAME | SYMBOL | DESCRIPTION |

|

|

|

|

7 | Receiver | RI | This bit, if high, indicates that the receiver is not enabled because either |

| Inhibited |

| an "Enable Receive to Page fnn" command was never issued, or a |

|

|

| packet has been deposited into the RAM buffer page fnn as specified by |

|

|

| the last "Enable Receive to Page fnn" command. No messages will be |

|

|

| received until this command is issued, and once the message has been |

|

|

| received, the RI bit is set, thereby inhibiting the receiver. The RI bit is |

|

|

| cleared by issuing an "Enable Receive to Page fnn" command. This bit, |

|

|

| when set, will cause an interrupt if the corresponding bit of the Interrupt |

|

|

| Mask Register (IMR) is also set. When this bit is set and another |

|

|

| station attempts to send a packet to this station, this station will send a |

|

|

| NAK. |

|

|

|

|

6,5 | (Reserved) |

| These bits are undefined. |

|

|

|

|

4 | Power On Reset | POR | This bit, if high, indicates that the COM20020 has been reset by either a |

|

|

| software reset, a hardware reset, or writing 00H to the Node ID |

|

|

| Register. The POR bit is cleared by the "Clear Flags" command. |

|

|

|

|

3 | Test | TEST | This bit is intended for test and diagnostic purposes. It is a logic "0" |

|

|

| under normal operating conditions. |

|

|

|

|

2 | Reconfiguration | RECON | This bit, if high, indicates that the Line Idle Timer has timed out because |

|

|

| the RXIN pin was idle for 82μS. The RECON bit is cleared during a |

|

|

| "Clear Flags" command. This bit, when set, will cause an interrupt if the |

|

|

| corresponding bit in the IMR is also set. The interrupt service routine |

|

|

| should consist of examining the MYRECON bit of the Diagnostic Status |

|

|

| Register to determine whether there are consecutive reconfigurations |

|

|

| caused by this node. |

|

|

|

|

1 | Transmitter | TMA | This bit, if high, indicates that the packet transmitted as a result of an |

| Message |

| "Enable Transmit from Page fnn" command has been acknowledged. |

| Acknowledged |

| This bit should only be considered valid after the TA bit (bit 0) is set. |

|

|

| Broadcast messages are never acknowledged. The TMA bit is cleared |

|

|

| by issuing the "Enable Transmit from Page fnn" command. |

|

|

|

|

0 | Transmitter | TA | This bit, if high, indicates that the transmitter is available for |

| Available |

| transmitting. This bit is set when the last byte of scheduled packet has |

|

|

| been transmitted out, or upon execution of a "Disable Transmitter" |

|

|

| command. The TA bit is cleared by issuing the "Enable Transmit from |

|

|

| Page fnn" command after the node next receives the token. This bit, |

|

|

| when set, will cause an interrupt if the corresponding bit in the IMR is |

|

|

| also set. |

|

|

|

|

25