M S B

T R I

T R I

R I

TA

P O R

T E S T

R E C O N

T M A

T M A

L S B

TTA

TTA

|

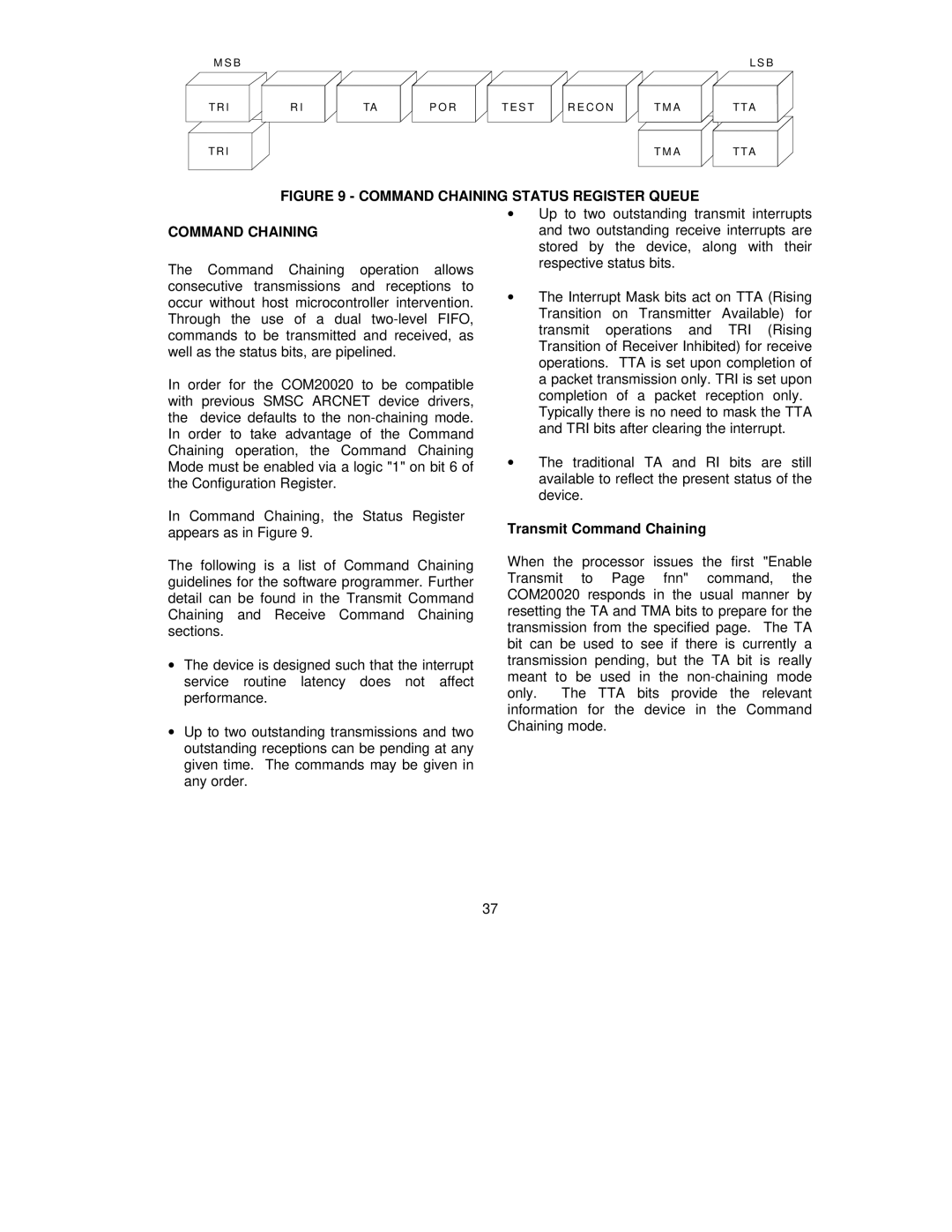

| FIGURE 9 - COMMAND CHAINING STATUS REGISTER QUEUE |

|

|

| ||||||||||||

|

|

|

|

|

|

|

| ∙ Up to two outstanding transmit interrupts | |||||||||

COMMAND CHAINING |

|

|

|

|

| and two outstanding receive interrupts are | |||||||||||

|

|

|

|

|

|

|

|

| stored by the device, along with their | ||||||||

The Command Chaining operation allows |

| respective status bits. |

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

| |||||||||

consecutive transmissions | and | receptions to | ∙ The Interrupt Mask bits act on TTA (Rising | ||||||||||||||

occur without host microcontroller intervention. | |||||||||||||||||

| Transition on | Transmitter | Available) for | ||||||||||||||

Through | the use of a dual | FIFO, |

| ||||||||||||||

| transmit | operations | and | TRI | (Rising | ||||||||||||

commands to be transmitted and received, as |

| ||||||||||||||||

| Transition of Receiver Inhibited) for receive | ||||||||||||||||

well as the status bits, are pipelined. |

|

|

| ||||||||||||||

|

|

| operations. TTA is set upon completion of | ||||||||||||||

|

|

|

|

|

|

|

|

| |||||||||

In | order | for the COM20020 to | be | compatible |

| a packet transmission only. TRI is set upon | |||||||||||

| completion of | a | packet reception | only. | |||||||||||||

with previous SMSC ARCNET | device | drivers, |

| ||||||||||||||

| Typically there is no need to mask the TTA | ||||||||||||||||

the device defaults to the |

| ||||||||||||||||

| and TRI bits after clearing the interrupt. | ||||||||||||||||

In order to take advantage of the Command |

| ||||||||||||||||

|

|

|

|

|

|

|

|

| |||||||||

Chaining | operation, | the Command Chaining | ∙ | The traditional | TA and RI | bits | are still | ||||||||||

Mode must be enabled via a logic "1" on bit 6 of | |||||||||||||||||

| available to reflect the present status of the | ||||||||||||||||

the Configuration Register. |

|

|

|

|

| ||||||||||||

|

|

|

|

| device. |

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

In Command Chaining, the Status Register | Transmit Command Chaining |

|

|

| |||||||||||||

appears as in Figure 9. |

|

|

|

|

|

|

| ||||||||||

The following is a list of Command Chaining | When the processor issues the first "Enable | ||||||||||||||||

guidelines for the software programmer. Further | Transmit to Page fnn" command, the | ||||||||||||||||

detail can be found in the Transmit Command | COM20020 responds in the usual manner by | ||||||||||||||||

Chaining and Receive Command Chaining | resetting the TA and TMA bits to prepare for the | ||||||||||||||||

sections. |

|

|

|

|

|

| transmission from the specified page. | The TA | |||||||||

|

|

|

|

|

|

|

| bit can be used to see if there is currently a | |||||||||

∙ | The device is designed such that the interrupt | transmission | pending, | but | the TA bit | is | really | ||||||||||

meant to be | used | in | the | mode | |||||||||||||

| service | routine | latency | does | not | affect | |||||||||||

| only. | The | TTA | bits provide | the | relevant | |||||||||||

| performance. |

|

|

|

|

| |||||||||||

|

|

|

|

|

| information for the device in the Command | |||||||||||

|

|

|

|

|

|

|

| ||||||||||

∙ | Up to two outstanding transmissions and two | Chaining mode. |

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

| |||||||||

outstanding receptions can be pending at any given time. The commands may be given in any order.

37