Key Features

Applications

Product Description

Table of contents

RF Data Buffering

Ordering Information General Information

ITU-T

Abbreviations

References

Features

Operating Conditions

Absolute Maximum Ratings

Parameter Min Max Units Condition

Parameter Min Typ Max Units Condition

Overall

Electrical Specifications

Transmit Section

Parameter Min Typ Max Unit Condition / Note

Receive Section

Rssi / Carrier Sense

If Section

Frequency Synthesizer Section

VDD

Digital Inputs/Outputs

Battery Monitor

Power Supply

Voltage Regulator

CC2420

Pin Pin Name Pin type Pin Description

Pin Assignment

Avddadc

Circuit Description

CC2420 simplified block diagram

CC2420

Application Circuit

Power supply decoupling and filtering

Input / output matching

Bias resistor

Description

Overview of external components

Transceiver

Transceiver

Bill of materials for the application circuits

Ieee 802.15.4 Modulation Format

Symbol Chip sequence C0, C1, C2, … , C31

Phase

Configuration Overview

SmartRF Studio user interface

Evaluation Software

13 4-wire Serial Configuration and Data Interface

Pin configuration

Register access

Parameter Symbol Min Max Units Conditions

SPI timing specification Status byte

RAM access

Configuration registers write and read operations via SPI

CC2420 RAM Memory Space Fifo access

Multiple SPI access

Address Byte Ordering Name Description

Microcontroller Interface and Pin Description

Configuration interface

Rxfifo overflow

Receive mode

Pin activity examples during receive

Demodulator, Symbol Synchroniser and Data Decision

Frame Format

Demodulator Simplified Block Diagram

MAC protocol data unit

Transmitted Synchronisation Header Length field

Format of the Frame Control Field FCF Frame check sequence

Buffered transmit mode

Buffered receive mode

RF Data Buffering

Fifop

Unbuffered, serial mode

Acknowledge Frames

Address Recognition

Acknowledge frame format

Radio control state machine

Radio control states

Keys

MAC Security Operations Encryption and Authentication

Nonce / counter

Ieee 802.15.4 Nonce

In-line security operations

CC2420 Security Flag Byte Stand-alone encryption

CTR mode encryption / decryption

CBC-MAC

21.7 CCM

Mode LMIC Time

Linear if and AGC Settings

Rssi / Energy Detection

Timing

Link Quality Indication

Value

RF Level dBm

Frequency and Channel Programming

Clear Channel Assessment

VCO and PLL Self-Calibration

Output Power Programming

Voltage Regulator

27.1 VCO

Voltage regulator, simplified schematic

Battery Monitor

Crystal Oscillator

Transmitter Test Modes

Input / Output Matching

Crystal oscillator component values

Unmodulated carrier

CC2420

Modulated spectrum plot

System Considerations and Guidelines

Battery operated systems

Low-cost systems

BER / PER measurements

Antenna Considerations

PCB Layout Recommendations

CC2420

Address Register Register type Description

Configuration Registers

Saes

Configuration registers overview

Bit Field Name Reset

Main 0x10 Main Control Register

XOSC16MBYPASS

MDMCTRL0 0x11 Modem Control Register

Reservedframemode Pancoordinator Adrdecode

CCAHYST20 CCAMODE10 Autocrc Autoack Preamblelength

Rssi 0x13 Rssi and CCA Status and Control Register

MDMCTRL1 0x12- Modem Control Register

CORRTHR40 Demodavgmode Modulationmode

RSSIVAL70

Txctrl 0x15 Transmit Control Register

Syncword 0x14 Sync Word

RXMIXBUFCUR10

RXCTRL0 0x16 Receive control register

RXCTRL1 0x17 Receive control register

Caldone Calrunning Locklength Lockstatus

Fsctrl 0x18 Frequency Synthesizer Control and Status

SECMODE10

SECCTRL0 0x19 Security Control Register

SECCTRL1 0x1A Security Control Register

Battmon 0x1B Battery Monitor Control register

Sectxl Secrxl

Battmonok Battmonen Battmonvoltage

IOCFG1 0x1D I/O Configuration Register

IOCFG0 0x1C I/O Configuration Register

Manfidl 0x1E Manufacturer ID, Lower 16 Bit

HSSDSRC20 SFDMUX40 CCAMUX40

Fsmtc 0x20 Finite state machine time constants

Manfidh 0x1F Manufacturer ID, Upper 16 Bit

Isused = is * Isandmask + Isormask

Manand 0x21 Manual signal and override register1

Agcctrl 0x23 AGC Control

Manor 0x22 Manual signal or override register

Vgagainoe

Lnamixgainmodeo

AGCTST0 0x24 AGC Test Register

AGCTST1 0x25 AGC Test Register

AGCTST2 0x26 AGC Test Register

FSTST0 0x27 Frequency Synthesizer Test Register

FSTST1 0x28 Frequency Synthesizer Test Register

FSTST2 0x29 Frequency Synthesizer Test Register

FSTST3 0x2A Frequency Synthesizer Test Register

Rxbpftst 0x2B Receiver Bandpass Filters Test Register

Fsmstate 0x2C Finite state machine information

Adcclockdisable

Adctst 0x2D ADC Test Register

Dactst 0x2E DAC Test Register

Toptst 0x2F Top Level Test Register

Oscillator must be running for accessing the Rxfifo

Txfifo 0x3E Transmit Fifo Byte register

Rxfifo 0x3F Receive Fifo Byte register

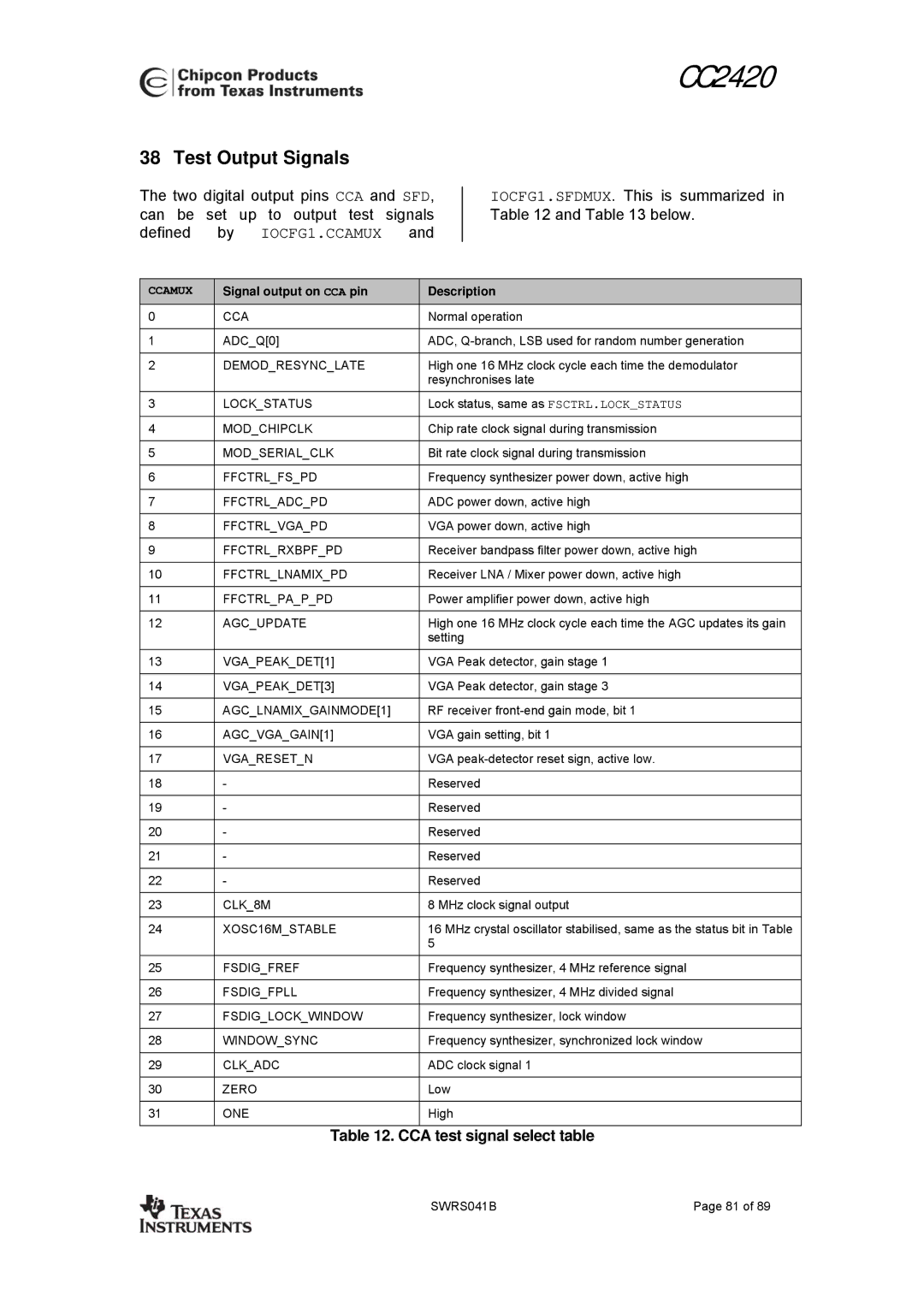

Test Output Signals

CCA test signal select table

Signal output on CCA pin Description

Signal output on SFD pin Description

SFD test signal select table

Quad Leadless Package QLP

Package Description QLP

Package thermal properties

Recommended layout for package QLP

Soldering information

Thermal resistance

40.4 Carrier tape and reel specification

40.3 Plastic tube specification

Tube Specification

Tape and Reel Specification

General Information

42.1 Document History

Revision Date Description/Changes

Product Status Definitions

Data Sheet Identification Product Status Definition

Address Information

TI Worldwide Technical Support Internet

Product Information Centers

2007, Texas Instruments. All rights reserved

Important Notice