CC2420

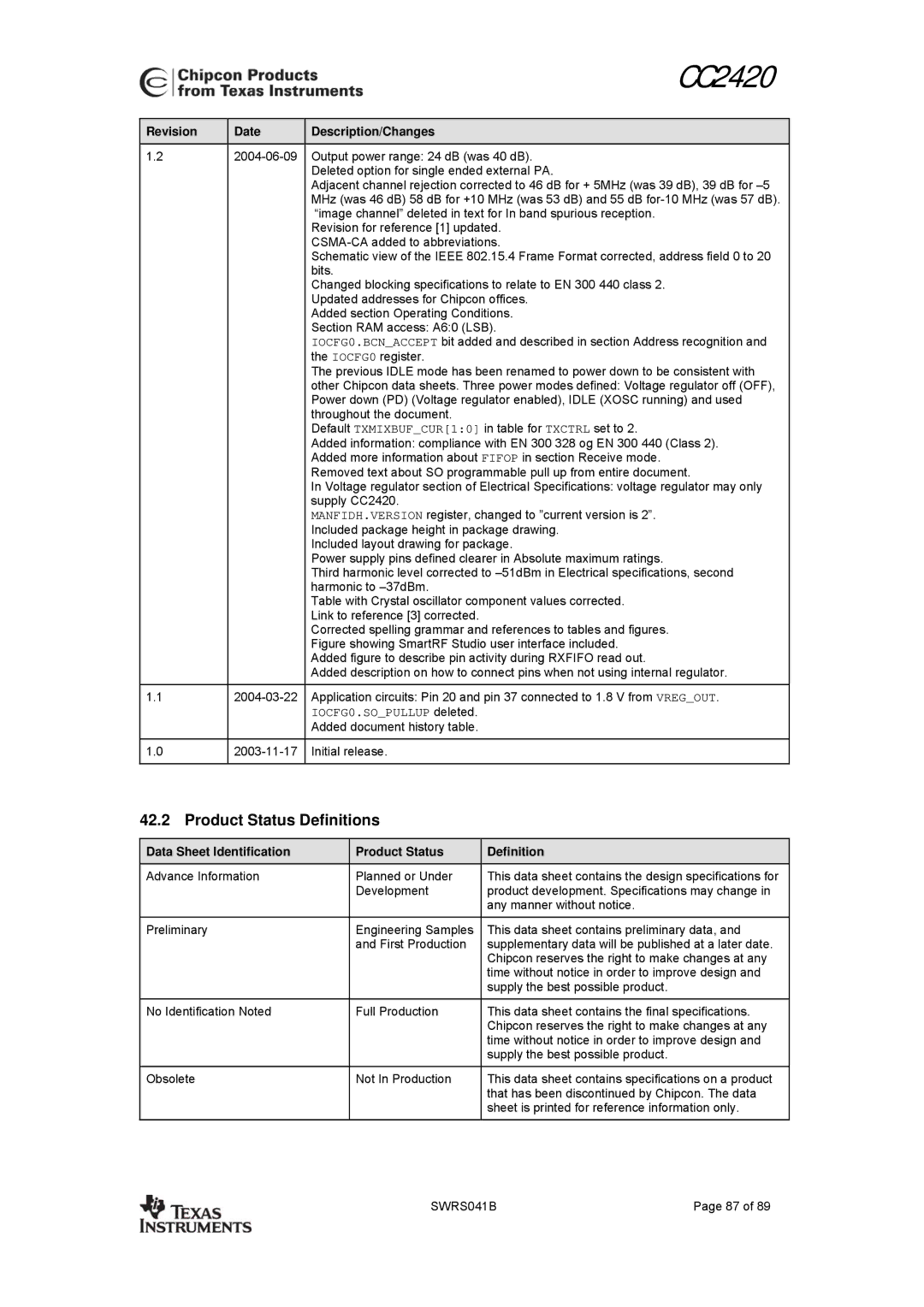

Revision | Date | Description/Changes |

1.2 | Output power range: 24 dB (was 40 dB). | |

|

| Deleted option for single ended external PA. |

|

| Adjacent channel rejection corrected to 46 dB for + 5MHz (was 39 dB), 39 dB for |

|

| MHz (was 46 dB) 58 dB for +10 MHz (was 53 dB) and 55 dB |

|

| “image channel” deleted in text for In band spurious reception. |

|

| Revision for reference [1] updated. |

|

| |

|

| Schematic view of the IEEE 802.15.4 Frame Format corrected, address field 0 to 20 |

|

| bits. |

|

| Changed blocking specifications to relate to EN 300 440 class 2. |

|

| Updated addresses for Chipcon offices. |

|

| Added section Operating Conditions. |

|

| Section RAM access: A6:0 (LSB). |

|

| IOCFG0.BCN_ACCEPT bit added and described in section Address recognition and |

|

| the IOCFG0 register. |

|

| The previous IDLE mode has been renamed to power down to be consistent with |

|

| other Chipcon data sheets. Three power modes defined: Voltage regulator off (OFF), |

|

| Power down (PD) (Voltage regulator enabled), IDLE (XOSC running) and used |

|

| throughout the document. |

|

| Default TXMIXBUF_CUR[1:0] in table for TXCTRL set to 2. |

|

| Added information: compliance with EN 300 328 og EN 300 440 (Class 2). |

|

| Added more information about FIFOP in section Receive mode. |

|

| Removed text about SO programmable pull up from entire document. |

|

| In Voltage regulator section of Electrical Specifications: voltage regulator may only |

|

| supply CC2420. |

|

| MANFIDH.VERSION register, changed to ”current version is 2”. |

|

| Included package height in package drawing. |

|

| Included layout drawing for package. |

|

| Power supply pins defined clearer in Absolute maximum ratings. |

|

| Third harmonic level corrected to |

|

| harmonic to |

|

| Table with Crystal oscillator component values corrected. |

|

| Link to reference [3] corrected. |

|

| Corrected spelling grammar and references to tables and figures. |

|

| Figure showing SmartRF Studio user interface included. |

|

| Added figure to describe pin activity during RXFIFO read out. |

|

| Added description on how to connect pins when not using internal regulator. |

|

|

|

1.1 | Application circuits: Pin 20 and pin 37 connected to 1.8 V from VREG_OUT. | |

|

| IOCFG0.SO_PULLUP deleted. |

|

| Added document history table. |

1.0 | Initial release. | |

|

|

|

42.2 Product Status Definitions

Data Sheet Identification | Product Status | Definition |

Advance Information | Planned or Under | This data sheet contains the design specifications for |

| Development | product development. Specifications may change in |

|

| any manner without notice. |

|

|

|

Preliminary | Engineering Samples | This data sheet contains preliminary data, and |

| and First Production | supplementary data will be published at a later date. |

|

| Chipcon reserves the right to make changes at any |

|

| time without notice in order to improve design and |

|

| supply the best possible product. |

|

|

|

No Identification Noted | Full Production | This data sheet contains the final specifications. |

|

| Chipcon reserves the right to make changes at any |

|

| time without notice in order to improve design and |

|

| supply the best possible product. |

|

|

|

Obsolete | Not In Production | This data sheet contains specifications on a product |

|

| that has been discontinued by Chipcon. The data |

|

| sheet is printed for reference information only. |

|

|

|

SWRS041B | Page 87 of 89 |