www.ti.com

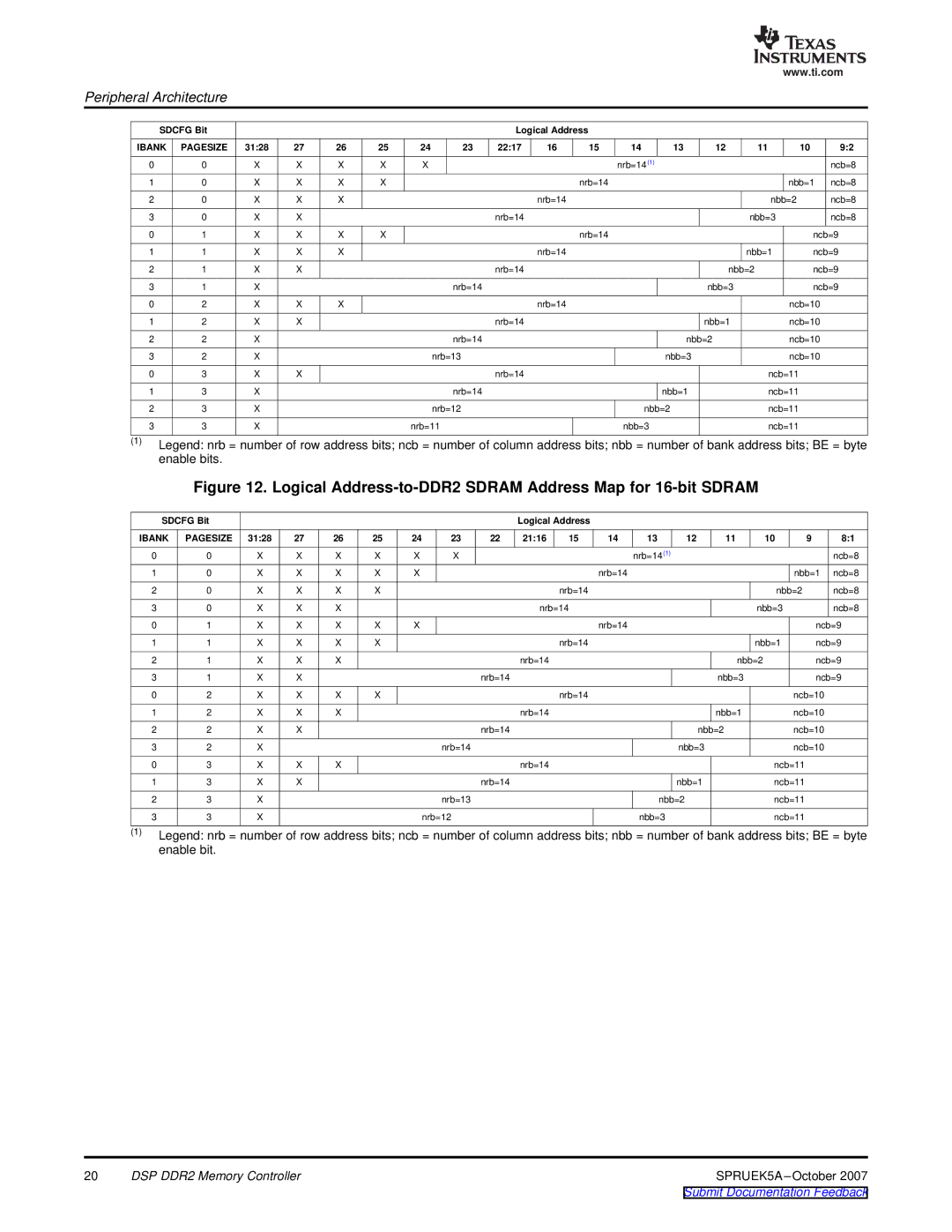

Peripheral Architecture

SDCFG Bit |

|

|

|

|

|

| Logical Address |

|

|

|

|

|

| |||

IBANK | PAGESIZE | 31:28 | 27 | 26 | 25 | 24 | 23 | 22:17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9:2 |

0 | 0 | X | X | X | X | X |

|

|

|

| nrb=14(1) |

|

|

|

| ncb=8 |

1 | 0 | X | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 ncb=8 | |

2 | 0 | X | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| nbb=2 | ncb=8 |

3 | 0 | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| nbb=3 | ncb=8 | |

0 | 1 | X | X | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| ncb=9 |

1 | 1 | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 | ncb=9 | |

2 | 1 | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=2 |

| ncb=9 | |

3 | 1 | X |

|

|

|

| nrb=14 |

|

|

|

|

| nbb=3 |

|

| ncb=9 |

0 | 2 | X | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| ncb=10 | |

1 | 2 | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 |

| ncb=10 | |

2 | 2 | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=2 |

| ncb=10 | ||

3 | 2 | X |

|

|

|

| nrb=13 |

|

|

|

| nbb=3 |

|

| ncb=10 | |

0 | 3 | X | X |

|

|

|

| nrb=14 |

|

|

|

|

|

| ncb=11 |

|

1 | 3 | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 |

|

| ncb=11 |

|

2 | 3 | X |

|

|

|

| nrb=12 |

|

|

| nbb=2 |

|

| ncb=11 |

| |

3 | 3 | X |

|

|

| nrb=11 |

|

|

| nbb=3 |

|

|

| ncb=11 |

| |

(1)Legend: nrb = number of row address bits; ncb = number of column address bits; nbb = number of bank address bits; BE = byte enable bits.

Figure 12. Logical Address-to-DDR2 SDRAM Address Map for 16-bit SDRAM

SDCFG Bit |

|

|

|

|

|

|

| Logical Address |

|

|

|

|

|

|

| ||

IBANK | PAGESIZE | 31:28 | 27 | 26 | 25 | 24 | 23 | 22 | 21:16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8:1 |

0 | 0 | X | X | X | X | X | X |

|

|

|

| nrb=14(1) |

|

|

|

| ncb=8 |

1 | 0 | X | X | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 ncb=8 | |

2 | 0 | X | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=2 | ncb=8 | |

3 | 0 | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=3 |

| ncb=8 | |

0 | 1 | X | X | X | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| ncb=9 |

1 | 1 | X | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 |

| ncb=9 |

2 | 1 | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=2 |

| ncb=9 | |

3 | 1 | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| nbb=3 |

|

| ncb=9 |

0 | 2 | X | X | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| ncb=10 | |

1 | 2 | X | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 |

| ncb=10 | |

2 | 2 | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=2 |

| ncb=10 | ||

3 | 2 | X |

|

|

|

| nrb=14 |

|

|

|

|

| nbb=3 |

|

| ncb=10 | |

0 | 3 | X | X | X |

|

|

|

| nrb=14 |

|

|

|

|

| ncb=11 |

| |

1 | 3 | X | X |

|

|

|

| nrb=14 |

|

|

|

| nbb=1 |

| ncb=11 |

| |

2 | 3 | X |

|

|

|

| nrb=13 |

|

|

|

| nbb=2 |

| ncb=11 |

| ||

3 | 3 | X |

|

|

|

| nrb=12 |

|

|

|

| nbb=3 |

|

| ncb=11 |

| |

(1)Legend: nrb = number of row address bits; ncb = number of column address bits; nbb = number of bank address bits; BE = byte enable bit.

20 | DSP DDR2 Memory Controller | SPRUEK5A |