www.ti.com

DDR2 Memory Controller Registers

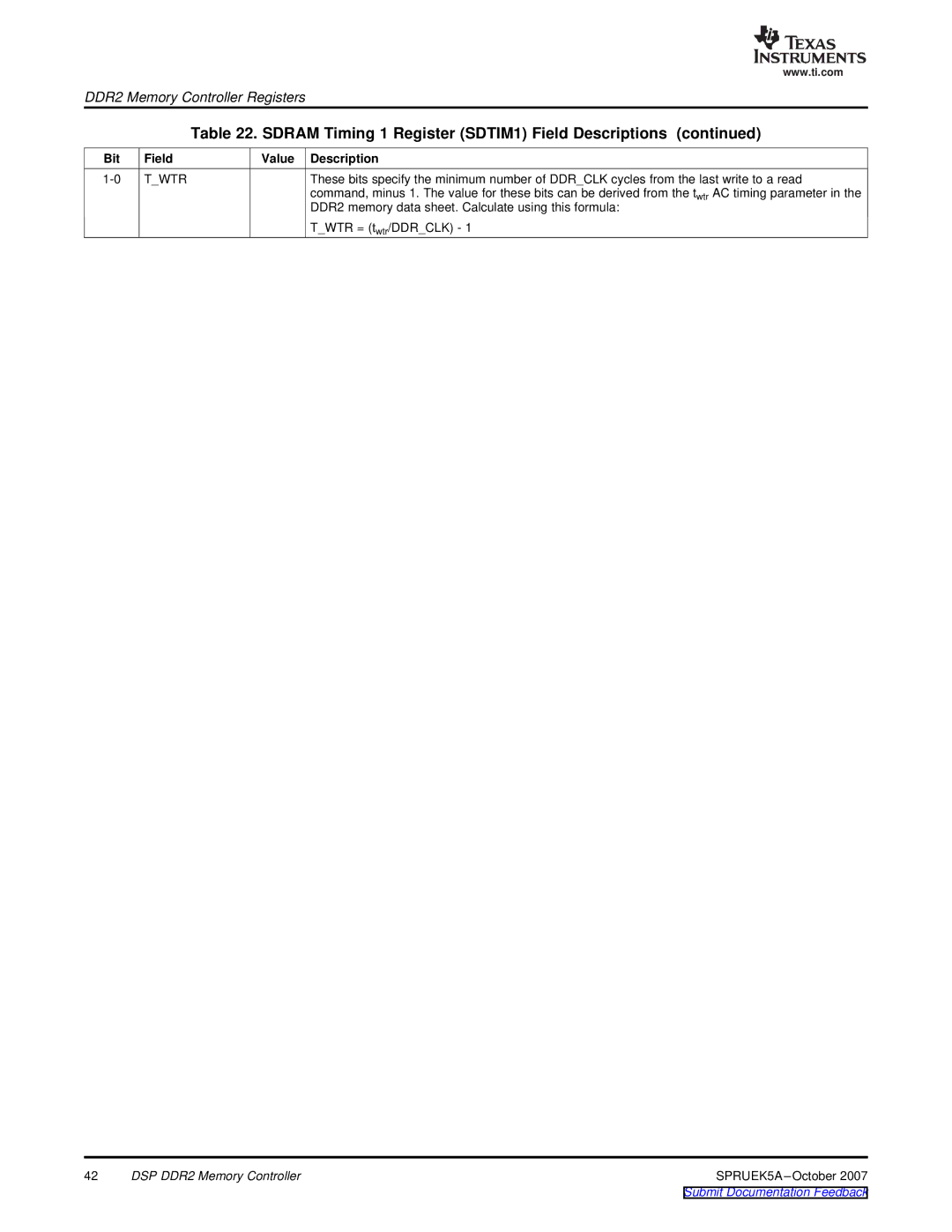

Table 22. SDRAM Timing 1 Register (SDTIM1) Field Descriptions (continued)

Bit | Field | Value Description |

T_WTR | These bits specify the minimum number of DDR_CLK cycles from the last write to a read | |

|

| command, minus 1. The value for these bits can be derived from the twtr AC timing parameter in the |

|

| DDR2 memory data sheet. Calculate using this formula: |

|

| T_WTR = (twtr/DDR_CLK) - 1 |

42 | DSP DDR2 Memory Controller | SPRUEK5A |