www.ti.com

Peripheral Architecture

2.4.4Deactivation (DCAB and DEAC)

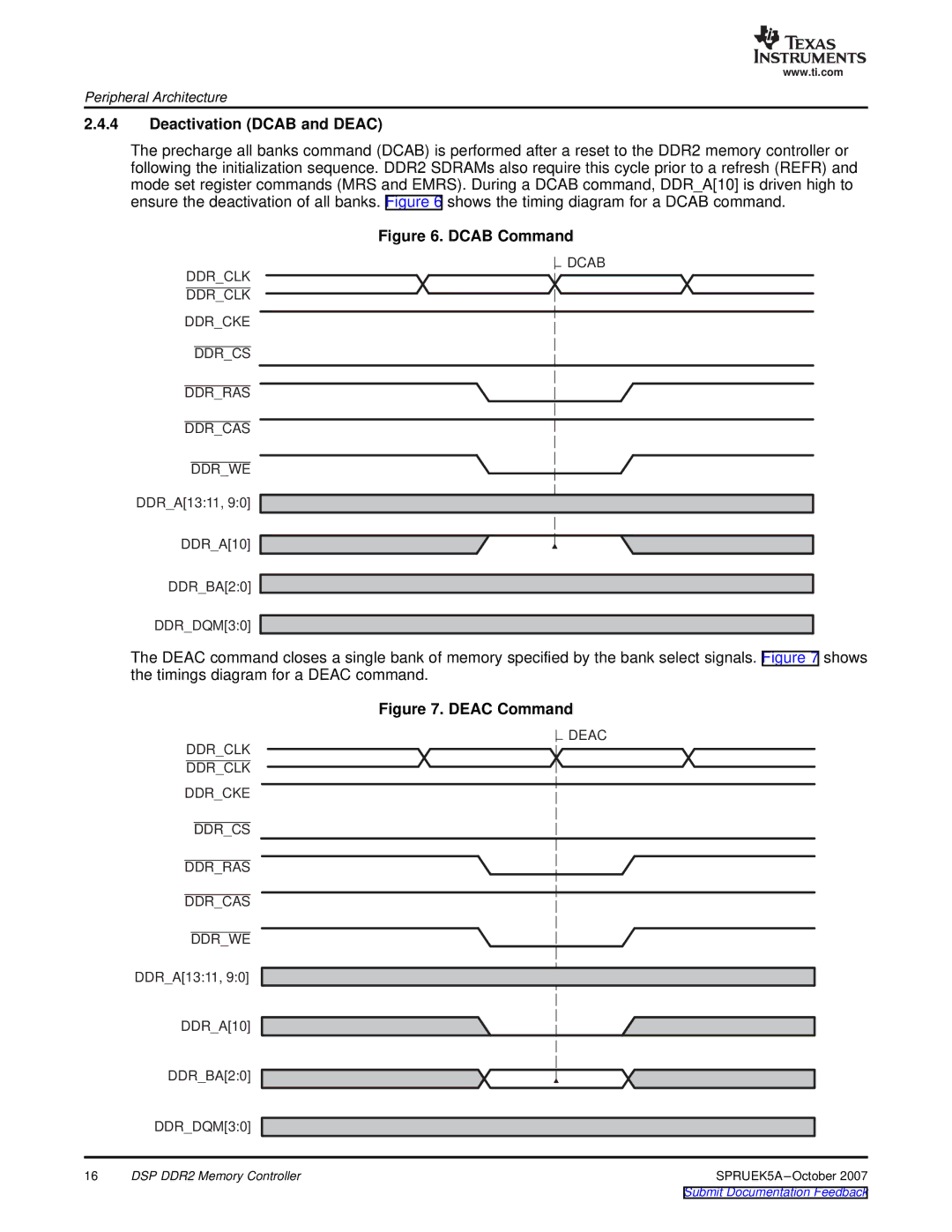

The precharge all banks command (DCAB) is performed after a reset to the DDR2 memory controller or following the initialization sequence. DDR2 SDRAMs also require this cycle prior to a refresh (REFR) and mode set register commands (MRS and EMRS). During a DCAB command, DDR_A[10] is driven high to ensure the deactivation of all banks. Figure 6 shows the timing diagram for a DCAB command.

Figure 6. DCAB Command

DCAB

DDR_CLK

DDR_CLK

DDR_CKE

DDR_CS

DDR_RAS

DDR_CAS

DDR_WE

DDR_A[13:11, 9:0]

DDR_A[10] ![]()

DDR_BA[2:0]

DDR_DQM[3:0]

The DEAC command closes a single bank of memory specified by the bank select signals. Figure 7 shows the timings diagram for a DEAC command.

Figure 7. DEAC Command

DEAC

DDR_CLK

DDR_CLK

DDR_CKE

DDR_CS

DDR_RAS

DDR_CAS

DDR_WE

DDR_A[13:11, 9:0]

DDR_A[10]

DDR_BA[2:0] ![]()

DDR_DQM[3:0]

16 | DSP DDR2 Memory Controller | SPRUEK5A |