www.ti.com

Peripheral Architecture

2.4.1Mode Register Set (MRS and EMRS)

DDR2 SDRAM contains mode and extended mode registers that configure the DDR2 memory for operation. These registers control burst type, burst length, CAS latency, DLL enable/disable,

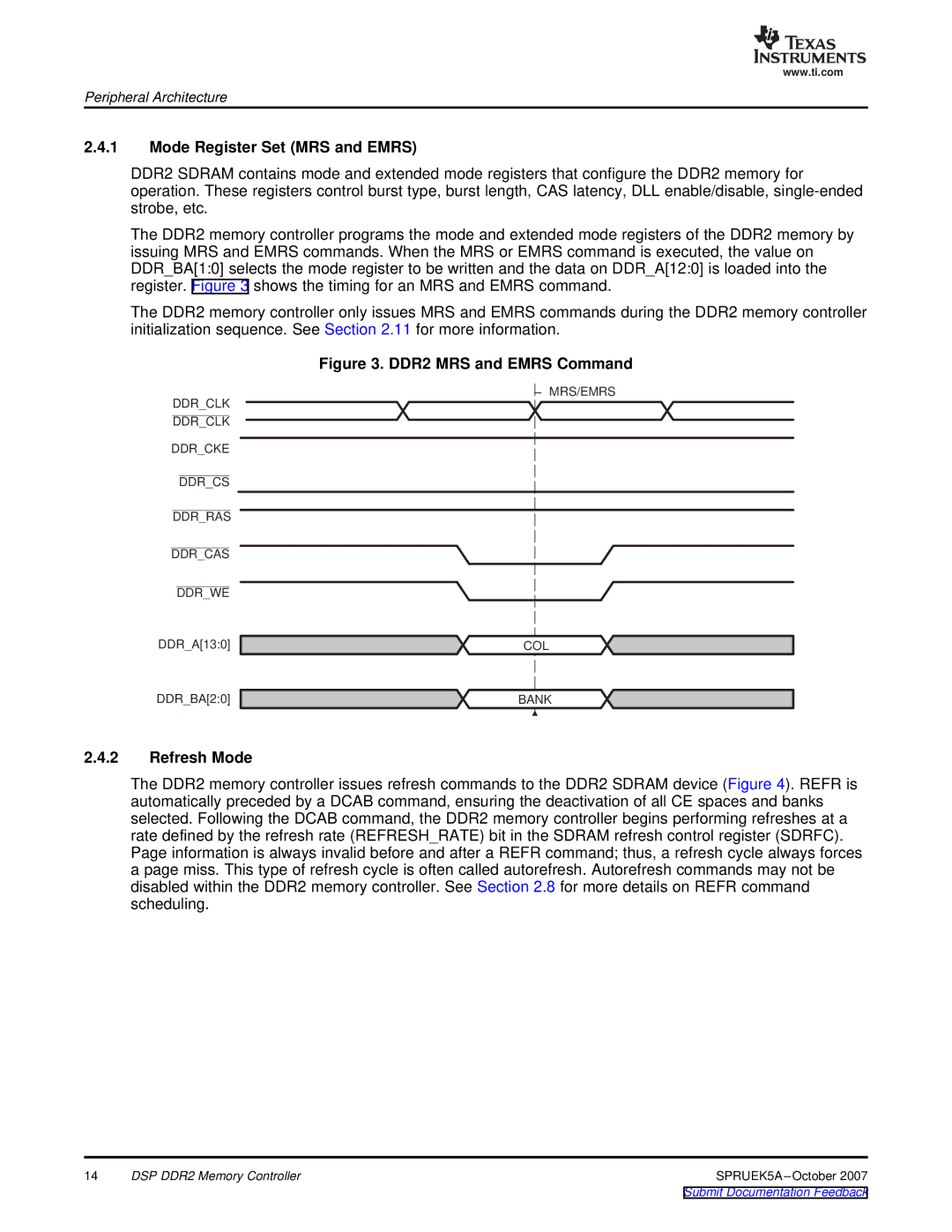

The DDR2 memory controller programs the mode and extended mode registers of the DDR2 memory by issuing MRS and EMRS commands. When the MRS or EMRS command is executed, the value on DDR_BA[1:0] selects the mode register to be written and the data on DDR_A[12:0] is loaded into the register. Figure 3 shows the timing for an MRS and EMRS command.

The DDR2 memory controller only issues MRS and EMRS commands during the DDR2 memory controller initialization sequence. See Section 2.11 for more information.

Figure 3. DDR2 MRS and EMRS Command

| DDR_CLK |

|

|

|

|

|

|

| MRS/EMRS |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

DDR_CLK |

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DDR_CKE |

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

| DDR_CS |

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| DDR_RAS |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DDR_CAS |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

| DDR_WE |

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

DDR_A[13:0] |

|

|

|

| COL |

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DDR_BA[2:0] |

|

|

|

|

| BANK |

|

|

|

| |||||||||||

2.4.2Refresh Mode

The DDR2 memory controller issues refresh commands to the DDR2 SDRAM device (Figure 4). REFR is automatically preceded by a DCAB command, ensuring the deactivation of all CE spaces and banks selected. Following the DCAB command, the DDR2 memory controller begins performing refreshes at a rate defined by the refresh rate (REFRESH_RATE) bit in the SDRAM refresh control register (SDRFC). Page information is always invalid before and after a REFR command; thus, a refresh cycle always forces a page miss. This type of refresh cycle is often called autorefresh. Autorefresh commands may not be disabled within the DDR2 memory controller. See Section 2.8 for more details on REFR command scheduling.

14 | DSP DDR2 Memory Controller | SPRUEK5A |