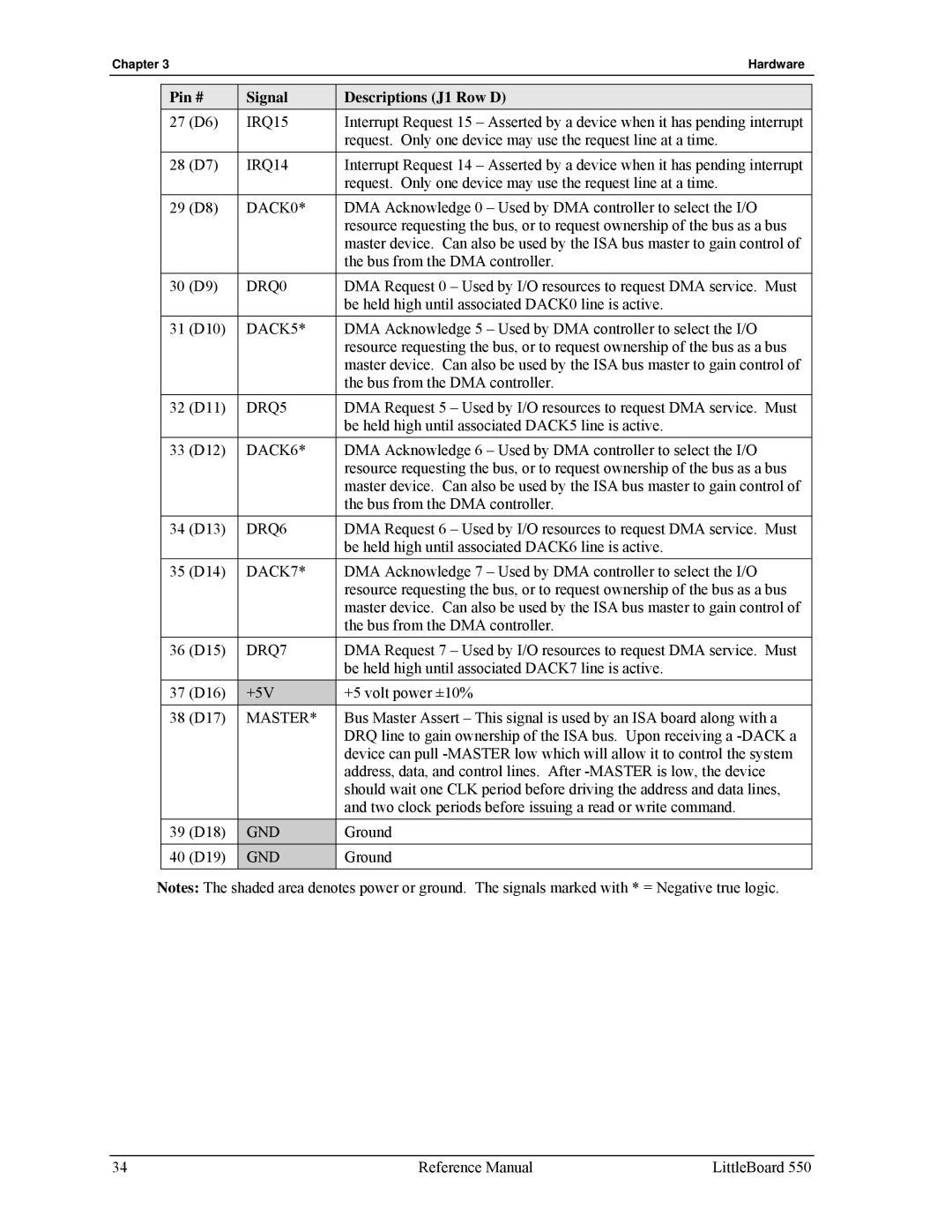

Chapter 3 | Hardware |

Pin # | Signal | Descriptions (J1 Row D) | |

27 | (D6) | IRQ15 | Interrupt Request 15 – Asserted by a device when it has pending interrupt |

|

|

| request. Only one device may use the request line at a time. |

28 | (D7) | IRQ14 | Interrupt Request 14 – Asserted by a device when it has pending interrupt |

|

|

| request. Only one device may use the request line at a time. |

29 | (D8) | DACK0* | DMA Acknowledge 0 – Used by DMA controller to select the I/O |

|

|

| resource requesting the bus, or to request ownership of the bus as a bus |

|

|

| master device. Can also be used by the ISA bus master to gain control of |

|

|

| the bus from the DMA controller. |

30 | (D9) | DRQ0 | DMA Request 0 – Used by I/O resources to request DMA service. Must |

|

|

| be held high until associated DACK0 line is active. |

31 | (D10) | DACK5* | DMA Acknowledge 5 – Used by DMA controller to select the I/O |

|

|

| resource requesting the bus, or to request ownership of the bus as a bus |

|

|

| master device. Can also be used by the ISA bus master to gain control of |

|

|

| the bus from the DMA controller. |

32 | (D11) | DRQ5 | DMA Request 5 – Used by I/O resources to request DMA service. Must |

|

|

| be held high until associated DACK5 line is active. |

33 | (D12) | DACK6* | DMA Acknowledge 6 – Used by DMA controller to select the I/O |

|

|

| resource requesting the bus, or to request ownership of the bus as a bus |

|

|

| master device. Can also be used by the ISA bus master to gain control of |

|

|

| the bus from the DMA controller. |

34 | (D13) | DRQ6 | DMA Request 6 – Used by I/O resources to request DMA service. Must |

|

|

| be held high until associated DACK6 line is active. |

35 | (D14) | DACK7* | DMA Acknowledge 7 – Used by DMA controller to select the I/O |

|

|

| resource requesting the bus, or to request ownership of the bus as a bus |

|

|

| master device. Can also be used by the ISA bus master to gain control of |

|

|

| the bus from the DMA controller. |

36 | (D15) | DRQ7 | DMA Request 7 – Used by I/O resources to request DMA service. Must |

|

|

| be held high until associated DACK7 line is active. |

37 | (D16) | +5V | +5 volt power ±10% |

38 | (D17) | MASTER* | Bus Master Assert – This signal is used by an ISA board along with a |

|

|

| DRQ line to gain ownership of the ISA bus. Upon receiving a |

|

|

| device can pull |

|

|

| address, data, and control lines. After |

|

|

| should wait one CLK period before driving the address and data lines, |

|

|

| and two clock periods before issuing a read or write command. |

39 | (D18) | GND | Ground |

40 | (D19) | GND | Ground |

Notes: The shaded area denotes power or ground. The signals marked with * = Negative true logic.

34 | Reference Manual | LittleBoard 550 |