AD9912

| ||

(dBc/Hz)NOISE | ||

| ||

PHASE | ||

| ||

| ||

| ||

| 100 |

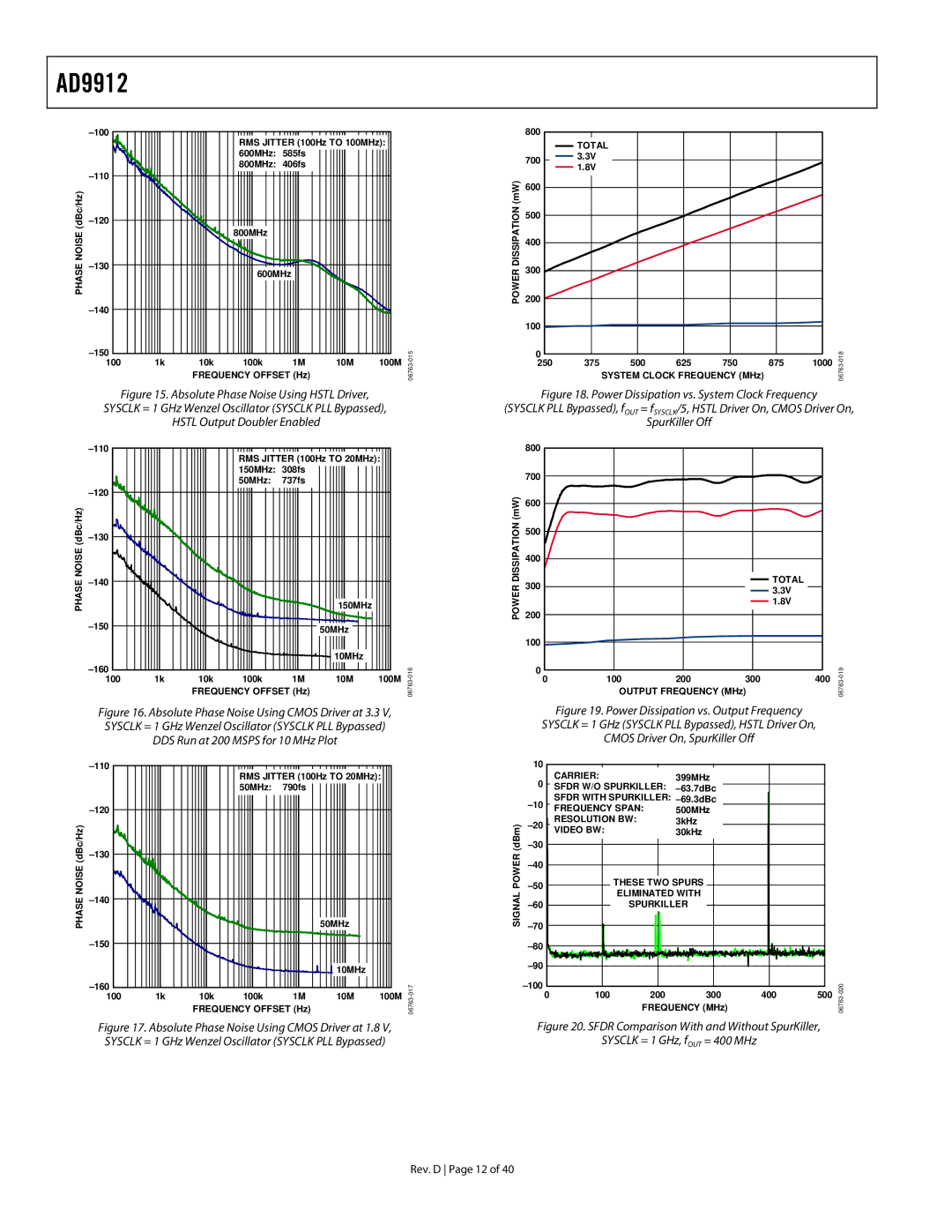

RMS JITTER (100Hz TO 100MHz): 600MHz: 585fs

800MHz: 406fs

800MHz

600MHz

1k | 10k | 100k | 1M | 10M | 100M |

FREQUENCY OFFSET (Hz)

| 800 |

|

|

|

|

|

|

|

|

| TOTAL |

|

|

|

|

| |

| 700 | 3.3V |

|

|

|

|

|

|

| 1.8V |

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

(mW) | 600 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

DISSIPATION | 500 |

|

|

|

|

|

|

|

400 |

|

|

|

|

|

|

| |

300 |

|

|

|

|

|

|

| |

POWER |

|

|

|

|

|

|

| |

200 |

|

|

|

|

|

|

| |

| 100 |

|

|

|

|

|

|

|

| 0 |

|

|

|

|

|

| |

| 250 | 375 | 500 | 625 | 750 | 875 | 1000 | |

| 06763 | |||||||

|

|

| SYSTEM CLOCK FREQUENCY (MHz) |

|

| |||

Figure 15. Absolute Phase Noise Using HSTL Driver,

SYSCLK = 1 GHz Wenzel Oscillator (SYSCLK PLL Bypassed),

HSTL Output Doubler Enabled

|

|

| RMS JITTER (100Hz TO 20MHz): |

| ||||

|

|

|

|

| ||||

|

|

|

| 150MHz: 308fs |

|

|

| |

|

|

| 50MHz: | 737fs |

|

|

| |

(dBc/Hz)NOISE |

|

|

|

|

|

|

| |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| |

PHASE |

|

|

|

|

|

|

| |

|

|

|

|

| 150MHz |

|

| |

|

|

|

|

| 50MHz |

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

| 10MHz |

|

|

|

|

|

|

|

|

| ||

| 100 | 1k | 10k | 100k | 1M | 10M | 100M | |

| 06763 | |||||||

|

|

| FREQUENCY OFFSET (Hz) |

|

| |||

Figure 16. Absolute Phase Noise Using CMOS Driver at 3.3 V, SYSCLK = 1 GHz Wenzel Oscillator (SYSCLK PLL Bypassed)

DDS Run at 200 MSPS for 10 MHz Plot

Figure 18. Power Dissipation vs. System Clock Frequency

(SYSCLK PLL Bypassed), fOUT = fSYSCLK/5, HSTL Driver On, CMOS Driver On,

SpurKiller Off

| 800 |

|

|

|

|

|

| 700 |

|

|

|

|

|

(mW) | 600 |

|

|

|

|

|

|

|

|

|

|

| |

DISSIPATION | 500 |

|

|

|

|

|

400 |

|

|

|

|

| |

300 |

|

|

| TOTAL |

| |

POWER |

|

|

|

| ||

|

|

| 3.3V |

| ||

|

|

|

|

| ||

|

|

|

| 1.8V |

| |

200 |

|

|

|

|

| |

| 100 |

|

|

|

|

|

| 0 |

|

|

|

| |

| 0 | 100 | 200 | 300 | 400 | |

| 06763 | |||||

|

| OUTPUT FREQUENCY (MHz) |

| |||

Figure 19. Power Dissipation vs. Output Frequency

SYSCLK = 1 GHz (SYSCLK PLL Bypassed), HSTL Driver On,

CMOS Driver On, SpurKiller Off

| ||

(dBc/Hz)NOISE | ||

| ||

PHASE | ||

| ||

| ||

| ||

| 100 |

RMS JITTER (100Hz TO 20MHz): 50MHz: 790fs

|

|

|

| 50MHz |

|

|

|

|

| 10MHz |

|

1k | 10k | 100k | 1M | 10M | 100M |

| FREQUENCY OFFSET (Hz) |

|

| ||

| 10 | CARRIER: |

|

|

|

|

|

| 0 |

| 399MHz |

|

|

| |

| SFDR W/O SPURKILLER: |

|

|

| |||

| SFDR WITH SPURKILLER: |

|

|

| |||

| FREQUENCY SPAN: | 500MHz |

|

|

| ||

|

|

|

|

| |||

(dBm) | RESOLUTION BW: | 3kHz |

|

|

| ||

VIDEO BW: |

| 30kHz |

|

|

| ||

|

|

|

|

| |||

| THESE TWO SPURS |

|

|

| |||

POWER |

|

|

|

| |||

|

|

|

|

|

|

| |

SIGNAL |

|

| ELIMINATED WITH |

|

|

| |

| SPURKILLER |

|

|

| |||

|

|

|

|

| |||

|

|

|

|

|

|

| |

|

|

|

|

|

|

| |

|

|

|

|

|

|

| |

|

|

|

|

|

| ||

| 0 | 100 | 200 | 300 | 400 | 500 | |

| 06763 | ||||||

|

|

| FREQUENCY (MHz) |

|

| ||

Figure 17. Absolute Phase Noise Using CMOS Driver at 1.8 V, SYSCLK = 1 GHz Wenzel Oscillator (SYSCLK PLL Bypassed)

Figure 20. SFDR Comparison With and Without SpurKiller,

SYSCLK = 1 GHz, fOUT = 400 MHz

Rev. D Page 12 of 40