AD9912

THEORY OF OPERATION

|

|

|

| OUT_CMOS |

|

|

|

|

| OUT |

|

|

|

| 2× | OUTB |

|

| ÷S |

|

| FDBK_IN |

|

|

|

|

|

| |

|

|

|

| FDBK_INB |

|

DIGITAL SYNTHESIS CORE |

|

| |||

|

| FREQUENCY |

|

| |

|

| TUNING WORD | DAC_OUT |

| |

|

|

|

| EXTERNAL | |

| CONTROL |

|

|

| |

|

| DDS/DAC | DAC_OUTB | ANALOG | |

| LOGIC |

| |||

|

|

| |||

|

|

|

|

| FILTER |

|

|

| LOW NOISE |

| EXTERNAL |

CONFIGURATION |

| CLOCK |

| LOOP | |

| MULTIPLIER |

| FILTER | ||

LOGIC |

|

|

| ||

|

|

|

|

| |

|

|

|

| AMP |

|

|

|

| SYSCLK PORT |

|

|

| DIGITAL |

|

|

| |

S1 TO S4 |

| SYSCLK SYSCLKB |

| 06763 | |

| INTERFACE |

|

| ||

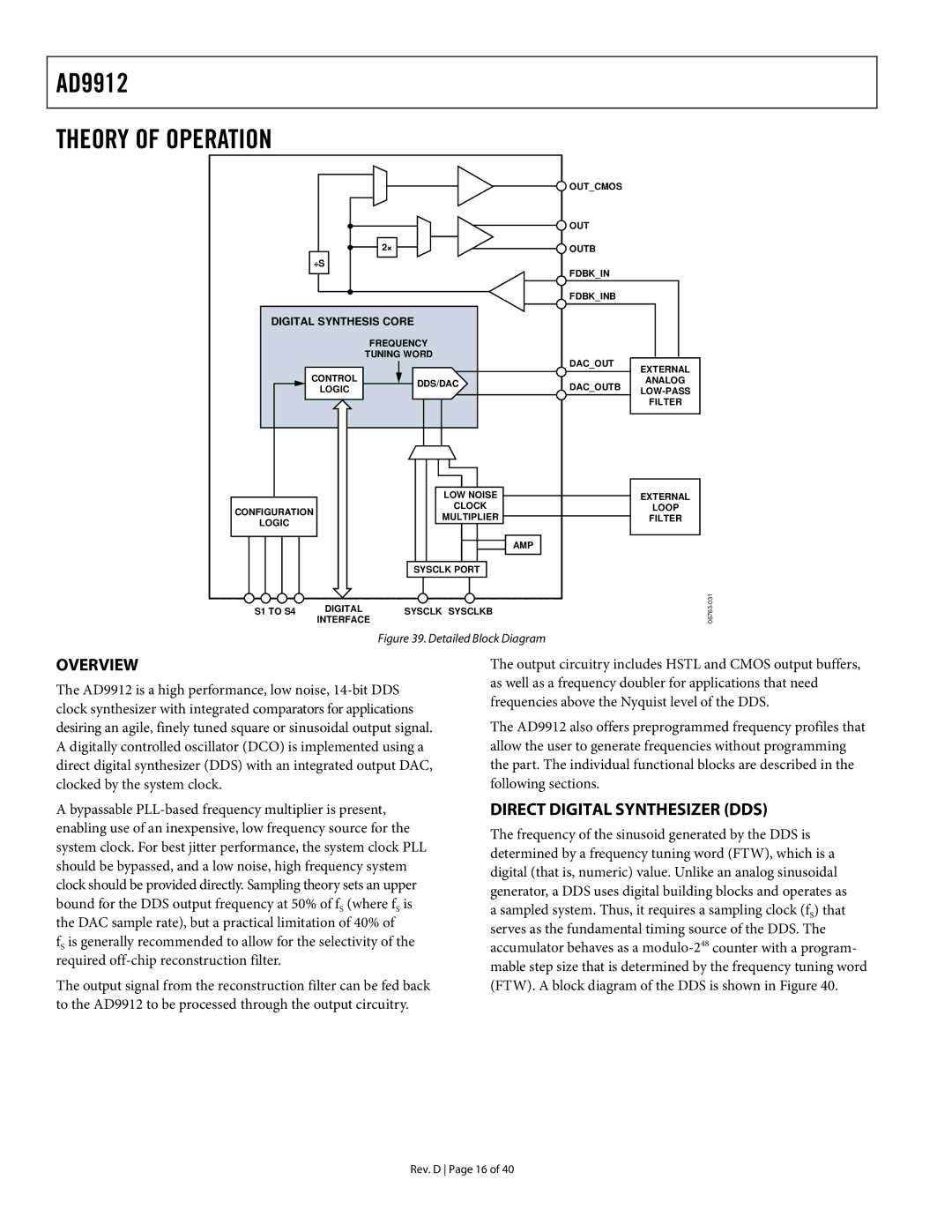

Figure 39. Detailed Block Diagram

OVERVIEW

The AD9912 is a high performance, low noise,

A bypassable

fS is generally recommended to allow for the selectivity of the required

The output signal from the reconstruction filter can be fed back to the AD9912 to be processed through the output circuitry.

The output circuitry includes HSTL and CMOS output buffers, as well as a frequency doubler for applications that need frequencies above the Nyquist level of the DDS.

The AD9912 also offers preprogrammed frequency profiles that allow the user to generate frequencies without programming the part. The individual functional blocks are described in the following sections.

DIRECT DIGITAL SYNTHESIZER (DDS)

The frequency of the sinusoid generated by the DDS is determined by a frequency tuning word (FTW), which is a digital (that is, numeric) value. Unlike an analog sinusoidal generator, a DDS uses digital building blocks and operates as a sampled system. Thus, it requires a sampling clock (fS) that serves as the fundamental timing source of the DDS. The accumulator behaves as a

Rev. D Page 16 of 40