AD9912

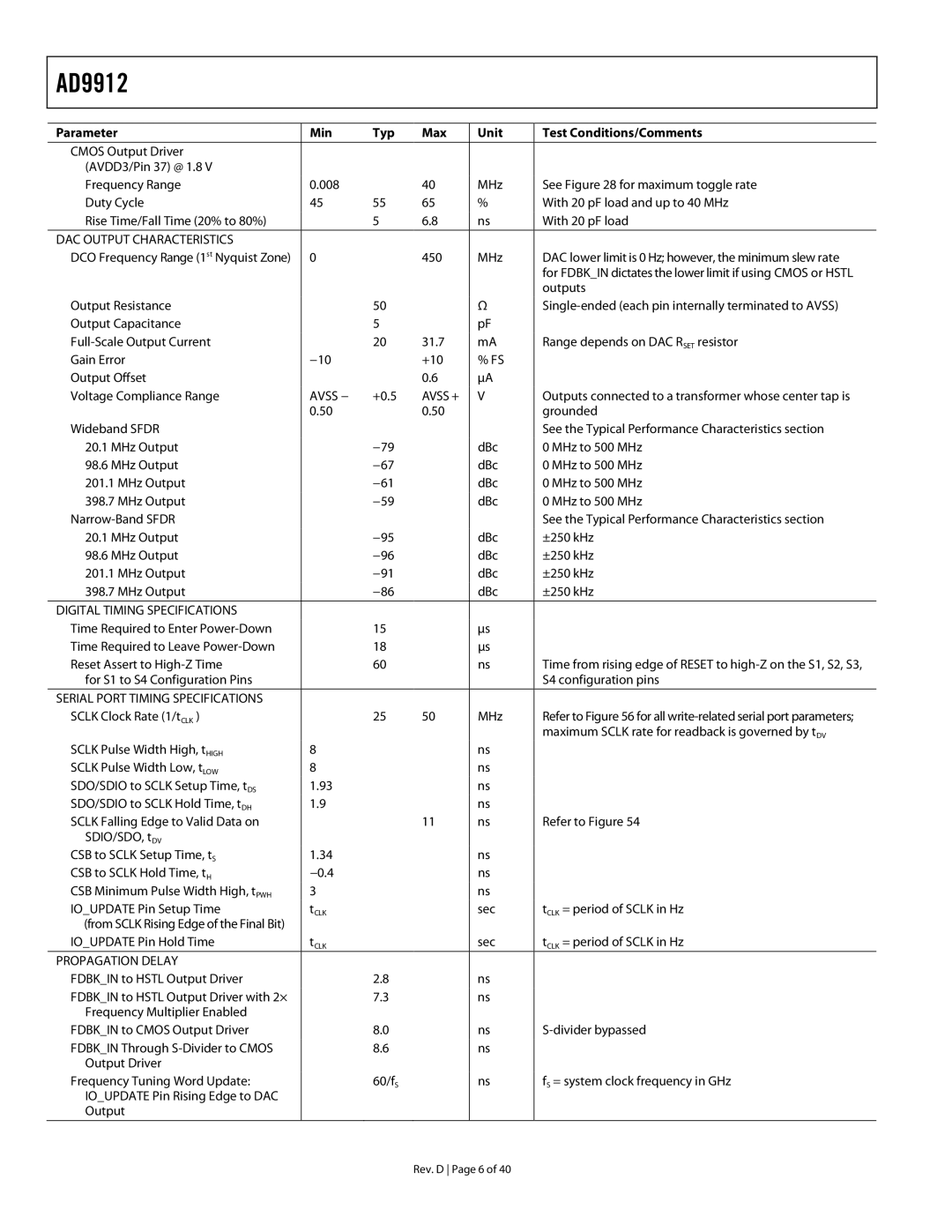

Parameter | Min | Typ | Max | Unit | Test Conditions/Comments |

|

|

|

|

|

|

CMOS Output Driver |

|

|

|

|

|

(AVDD3/Pin 37) @ 1.8 V |

|

|

|

|

|

Frequency Range | 0.008 |

| 40 | MHz | See Figure 28 for maximum toggle rate |

Duty Cycle | 45 | 55 | 65 | % | With 20 pF load and up to 40 MHz |

Rise Time/Fall Time (20% to 80%) |

| 5 | 6.8 | ns | With 20 pF load |

DAC OUTPUT CHARACTERISTICS |

|

|

|

|

|

DCO Frequency Range (1st Nyquist Zone) | 0 |

| 450 | MHz | DAC lower limit is 0 Hz; however, the minimum slew rate |

|

|

|

|

| for FDBK_IN dictates the lower limit if using CMOS or HSTL |

|

|

|

|

| outputs |

Output Resistance |

| 50 |

| Ω | |

Output Capacitance |

| 5 |

| pF |

|

| 20 | 31.7 | mA | Range depends on DAC RSET resistor | |

Gain Error | −10 |

| +10 | % FS |

|

Output Offset |

|

| 0.6 | μA |

|

Voltage Compliance Range | AVSS − | +0.5 | AVSS + | V | Outputs connected to a transformer whose center tap is |

| 0.50 |

| 0.50 |

| grounded |

Wideband SFDR |

|

|

|

| See the Typical Performance Characteristics section |

20.1 MHz Output |

| −79 |

| dBc | 0 MHz to 500 MHz |

98.6 MHz Output |

| −67 |

| dBc | 0 MHz to 500 MHz |

201.1 MHz Output |

| −61 |

| dBc | 0 MHz to 500 MHz |

398.7 MHz Output |

| −59 |

| dBc | 0 MHz to 500 MHz |

|

|

|

| See the Typical Performance Characteristics section | |

20.1 MHz Output |

| −95 |

| dBc | ±250 kHz |

98.6 MHz Output |

| −96 |

| dBc | ±250 kHz |

201.1 MHz Output |

| −91 |

| dBc | ±250 kHz |

398.7 MHz Output |

| −86 |

| dBc | ±250 kHz |

|

|

|

|

|

|

DIGITAL TIMING SPECIFICATIONS |

|

|

|

|

|

Time Required to Enter |

| 15 |

| µs |

|

Time Required to Leave |

| 18 |

| µs |

|

Reset Assert to |

| 60 |

| ns | Time from rising edge of RESET to |

for S1 to S4 Configuration Pins |

|

|

|

| S4 configuration pins |

SERIAL PORT TIMING SPECIFICATIONS |

|

|

|

|

|

SCLK Clock Rate (1/tCLK ) |

| 25 | 50 | MHz | Refer to Figure 56 for all |

|

|

|

|

| maximum SCLK rate for readback is governed by tDV |

SCLK Pulse Width High, tHIGH | 8 |

|

| ns |

|

SCLK Pulse Width Low, tLOW | 8 |

|

| ns |

|

SDO/SDIO to SCLK Setup Time, tDS | 1.93 |

|

| ns |

|

SDO/SDIO to SCLK Hold Time, tDH | 1.9 |

|

| ns |

|

SCLK Falling Edge to Valid Data on |

|

| 11 | ns | Refer to Figure 54 |

SDIO/SDO, tDV |

|

|

|

|

|

CSB to SCLK Setup Time, tS | 1.34 |

|

| ns |

|

CSB to SCLK Hold Time, tH | −0.4 |

|

| ns |

|

CSB Minimum Pulse Width High, tPWH | 3 |

|

| ns |

|

IO_UPDATE Pin Setup Time | tCLK |

|

| sec | tCLK = period of SCLK in Hz |

(from SCLK Rising Edge of the Final Bit) |

|

|

|

|

|

IO_UPDATE Pin Hold Time | tCLK |

|

| sec | tCLK = period of SCLK in Hz |

PROPAGATION DELAY |

|

|

|

|

|

FDBK_IN to HSTL Output Driver |

| 2.8 |

| ns |

|

FDBK_IN to HSTL Output Driver with 2× |

| 7.3 |

| ns |

|

Frequency Multiplier Enabled |

|

|

|

|

|

FDBK_IN to CMOS Output Driver |

| 8.0 |

| ns | |

FDBK_IN Through |

| 8.6 |

| ns |

|

Output Driver |

|

|

|

|

|

Frequency Tuning Word Update: |

| 60/fS |

| ns | fS = system clock frequency in GHz |

IO_UPDATE Pin Rising Edge to DAC |

|

|

|

|

|

Output |

|

|

|

|

|

Rev. D Page 6 of 40