AD9912

SYSCLK PLL Multiplier

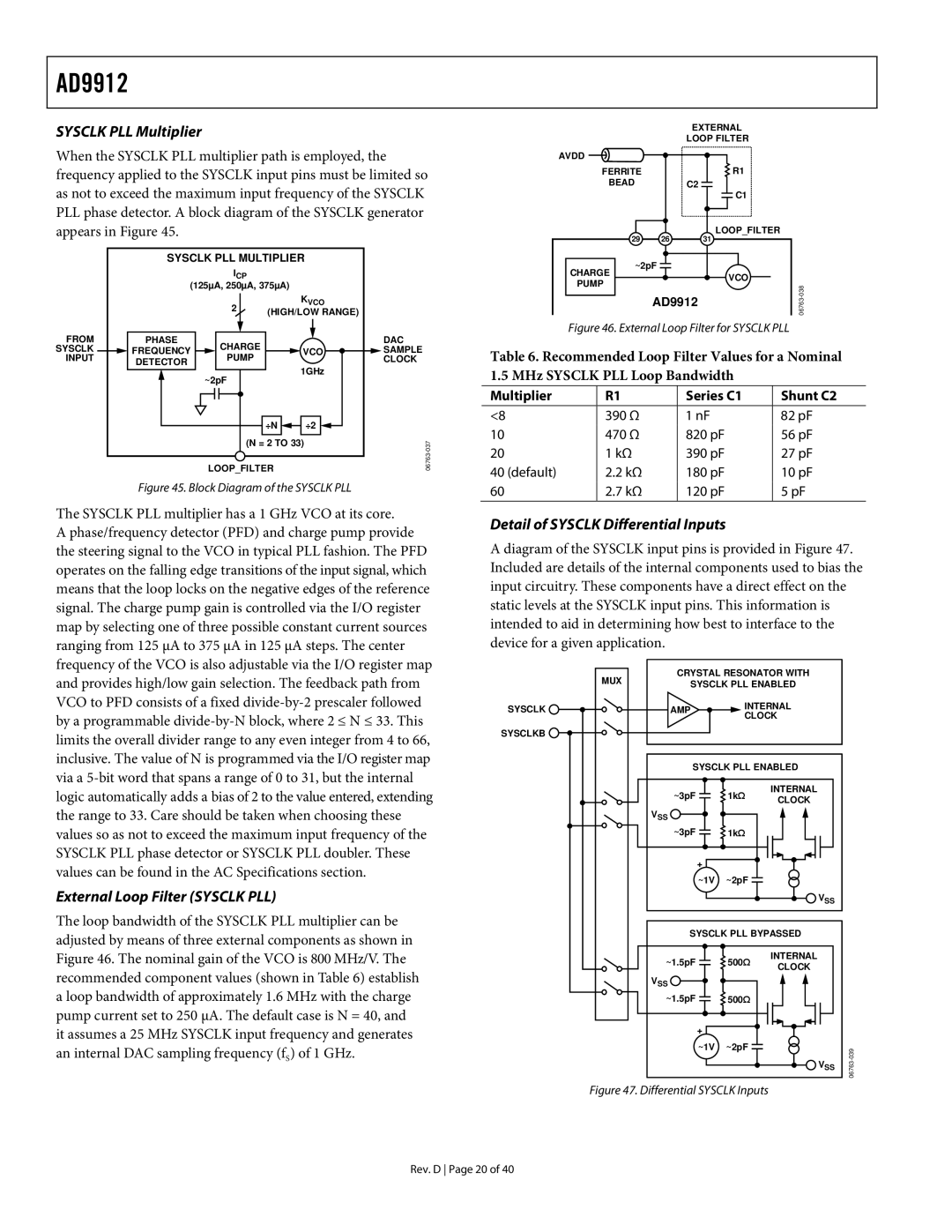

When the SYSCLK PLL multiplier path is employed, the frequency applied to the SYSCLK input pins must be limited so as not to exceed the maximum input frequency of the SYSCLK PLL phase detector. A block diagram of the SYSCLK generator appears in Figure 45.

|

|

|

|

| SYSCLK PLL MULTIPLIER |

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

| ICP |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| (125µA, 250µA, 375µA) |

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

| 2 |

|

|

|

|

|

| KVCO |

|

| |||||||||

|

|

|

|

|

|

|

| (HIGH/LOW RANGE) |

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

FROM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| PHASE |

|

|

|

| CHARGE |

|

|

|

|

|

|

|

|

|

|

| DAC | |||||

SYSCLK |

|

|

| FREQUENCY |

|

|

|

|

|

|

|

| VCO |

|

|

|

| SAMPLE | ||||||

INPUT |

|

| DETECTOR |

|

|

|

| PUMP |

|

|

|

| 1GHz |

|

| CLOCK | ||||||||

|

|

|

|

|

|

| ~2pF |

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ÷N |

|

|

| ÷2 |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| (N = 2 TO 33) | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| LOOP_FILTER |

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

Figure 45. Block Diagram of the SYSCLK PLL

The SYSCLK PLL multiplier has a 1 GHz VCO at its core.

A phase/frequency detector (PFD) and charge pump provide the steering signal to the VCO in typical PLL fashion. The PFD operates on the falling edge transitions of the input signal, which means that the loop locks on the negative edges of the reference signal. The charge pump gain is controlled via the I/O register map by selecting one of three possible constant current sources ranging from 125 μA to 375 μA in 125 μA steps. The center frequency of the VCO is also adjustable via the I/O register map

|

|

| EXTERNAL |

|

|

|

| LOOP FILTER |

|

AVDD |

|

|

|

|

FERRITE |

| R1 |

| |

BEAD |

| C2 |

| |

|

|

| C1 |

|

| 29 | 26 | LOOP_FILTER |

|

| 31 |

| ||

CHARGE | ~2pF | VCO |

| |

|

|

| ||

PUMP |

|

| ||

|

|

| ||

|

| AD9912 | ||

|

| 06763 | ||

|

|

|

| |

Figure 46. External Loop Filter for SYSCLK PLL

Table 6. Recommended Loop Filter Values for a Nominal 1.5 MHz SYSCLK PLL Loop Bandwidth

Multiplier | R1 | Series C1 | Shunt C2 |

<8 | 390 Ω | 1 nF | 82 pF |

10 | 470 Ω | 820 pF | 56 pF |

20 | 1 kΩ | 390 pF | 27 pF |

40 (default) | 2.2 kΩ | 180 pF | 10 pF |

60 | 2.7 kΩ | 120 pF | 5 pF |

Detail of SYSCLK Differential Inputs

A diagram of the SYSCLK input pins is provided in Figure 47. Included are details of the internal components used to bias the input circuitry. These components have a direct effect on the static levels at the SYSCLK input pins. This information is intended to aid in determining how best to interface to the device for a given application.

and provides high/low gain selection. The feedback path from VCO to PFD consists of a fixed

External Loop Filter (SYSCLK PLL)

The loop bandwidth of the SYSCLK PLL multiplier can be adjusted by means of three external components as shown in Figure 46. The nominal gain of the VCO is 800 MHz/V. The recommended component values (shown in Table 6) establish a loop bandwidth of approximately 1.6 MHz with the charge pump current set to 250 μA. The default case is N = 40, and it assumes a 25 MHz SYSCLK input frequency and generates an internal DAC sampling frequency (fS) of 1 GHz.

SYSCLK ![]()

SYSCLKB ![]()

MUX | CRYSTAL RESONATOR WITH |

| ||

SYSCLK PLL ENABLED |

| |||

| AMP | INTERNAL |

| |

| CLOCK |

| ||

|

|

| ||

| SYSCLK PLL ENABLED |

| ||

| ~3pF | 1kΩ | INTERNAL |

|

| CLOCK |

| ||

|

|

|

| |

| VSS |

|

|

|

| ~3pF | 1kΩ |

|

|

| + |

|

|

|

| ~1V | ~2pF |

|

|

|

|

| VSS |

|

| SYSCLK PLL BYPASSED |

| ||

| ~1.5pF | 500Ω | INTERNAL |

|

| CLOCK |

| ||

|

|

|

| |

| VSS |

|

|

|

| ~1.5pF | 500Ω |

|

|

| + |

|

|

|

| ~1V | ~2pF |

| |

|

|

| VSS | |

|

|

| 06763 | |

Figure 47. Differential SYSCLK Inputs

Rev. D Page 20 of 40