AD9912

POWER-UP

POWER-ON RESET

On initial

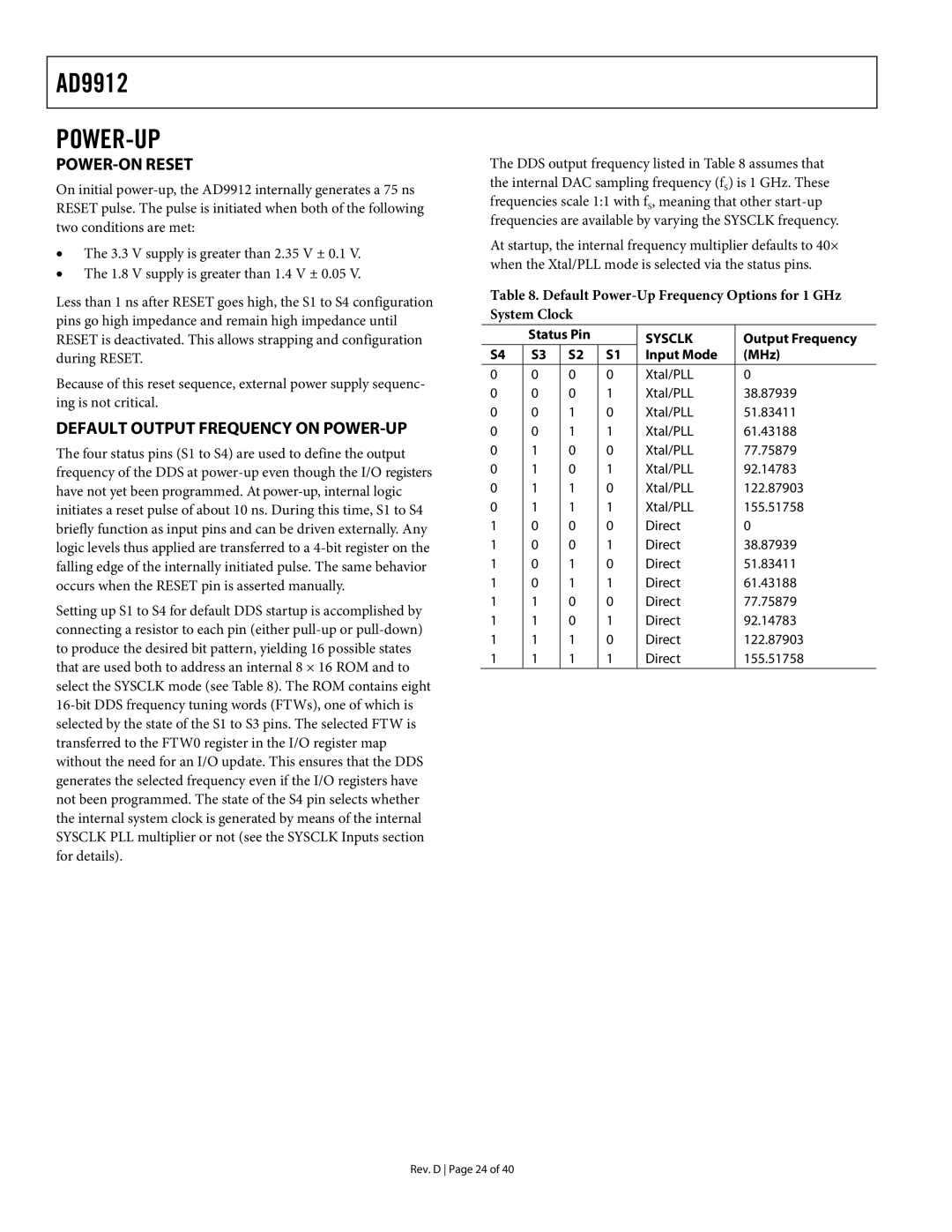

The DDS output frequency listed in Table 8 assumes that the internal DAC sampling frequency (fS) is 1 GHz. These frequencies scale 1:1 with fS, meaning that other

•The 3.3 V supply is greater than 2.35 V ± 0.1 V.

•The 1.8 V supply is greater than 1.4 V ± 0.05 V.

At startup, the internal frequency multiplier defaults to 40× when the Xtal/PLL mode is selected via the status pins.

Less than 1 ns after RESET goes high, the S1 to S4 configuration pins go high impedance and remain high impedance until RESET is deactivated. This allows strapping and configuration during RESET.

Because of this reset sequence, external power supply sequenc- ing is not critical.

DEFAULT OUTPUT FREQUENCY ON POWER-UP

The four status pins (S1 to S4) are used to define the output frequency of the DDS at

Setting up S1 to S4 for default DDS startup is accomplished by connecting a resistor to each pin (either

Table 8. Default Power-Up Frequency Options for 1 GHz System Clock

| Status Pin |

| SYSCLK | Output Frequency | |

S4 | S3 | S2 | S1 | Input Mode | (MHz) |

0 | 0 | 0 | 0 | Xtal/PLL | 0 |

0 | 0 | 0 | 1 | Xtal/PLL | 38.87939 |

0 | 0 | 1 | 0 | Xtal/PLL | 51.83411 |

0 | 0 | 1 | 1 | Xtal/PLL | 61.43188 |

0 | 1 | 0 | 0 | Xtal/PLL | 77.75879 |

0 | 1 | 0 | 1 | Xtal/PLL | 92.14783 |

0 | 1 | 1 | 0 | Xtal/PLL | 122.87903 |

0 | 1 | 1 | 1 | Xtal/PLL | 155.51758 |

1 | 0 | 0 | 0 | Direct | 0 |

1 | 0 | 0 | 1 | Direct | 38.87939 |

1 | 0 | 1 | 0 | Direct | 51.83411 |

1 | 0 | 1 | 1 | Direct | 61.43188 |

1 | 1 | 0 | 0 | Direct | 77.75879 |

1 | 1 | 0 | 1 | Direct | 92.14783 |

1 | 1 | 1 | 0 | Direct | 122.87903 |

1 | 1 | 1 | 1 | Direct | 155.51758 |

|

|

|

|

|

|

Rev. D Page 24 of 40