|

| AD9912 |

|

|

|

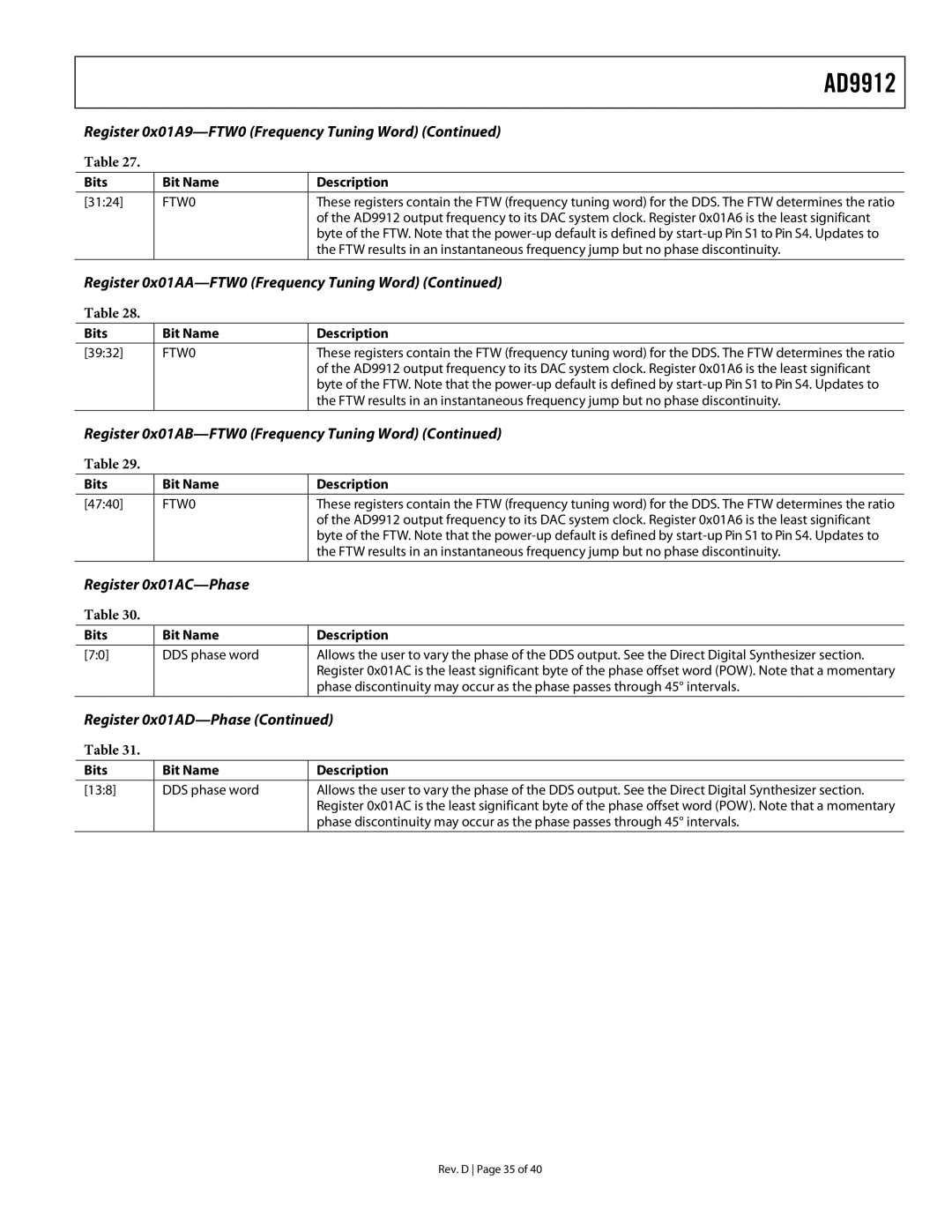

Register | ||

Table 27. |

|

|

Bits | Bit Name | Description |

[31:24] | FTW0 | These registers contain the FTW (frequency tuning word) for the DDS. The FTW determines the ratio |

|

| of the AD9912 output frequency to its DAC system clock. Register 0x01A6 is the least significant |

|

| byte of the FTW. Note that the |

|

| the FTW results in an instantaneous frequency jump but no phase discontinuity. |

Register | ||

Table 28. |

|

|

Bits | Bit Name | Description |

|

|

|

[39:32] | FTW0 | These registers contain the FTW (frequency tuning word) for the DDS. The FTW determines the ratio |

|

| of the AD9912 output frequency to its DAC system clock. Register 0x01A6 is the least significant |

|

| byte of the FTW. Note that the |

|

| the FTW results in an instantaneous frequency jump but no phase discontinuity. |

|

|

|

Register | ||

Table 29. |

|

|

Bits | Bit Name | Description |

[47:40] | FTW0 | These registers contain the FTW (frequency tuning word) for the DDS. The FTW determines the ratio |

|

| of the AD9912 output frequency to its DAC system clock. Register 0x01A6 is the least significant |

|

| byte of the FTW. Note that the |

|

| the FTW results in an instantaneous frequency jump but no phase discontinuity. |

|

|

|

Register |

| |

Table 30. |

|

|

Bits | Bit Name | Description |

|

|

|

[7:0] | DDS phase word | Allows the user to vary the phase of the DDS output. See the Direct Digital Synthesizer section. |

|

| Register 0x01AC is the least significant byte of the phase offset word (POW). Note that a momentary |

|

| phase discontinuity may occur as the phase passes through 45° intervals. |

|

|

|

Register | ||

Table 31. |

|

|

Bits | Bit Name | Description |

[13:8] | DDS phase word | Allows the user to vary the phase of the DDS output. See the Direct Digital Synthesizer section. |

|

| Register 0x01AC is the least significant byte of the phase offset word (POW). Note that a momentary |

|

| phase discontinuity may occur as the phase passes through 45° intervals. |

Rev. D Page 35 of 40