AD9912

|

| PHASE |

|

| DAC | DAC_RSET | |||

| OFFSET |

|

| REGISTERS |

| ||||

|

|

| 48 |

|

|

|

| AND LOGIC |

|

|

|

|

| 14 |

|

|

|

| |

FREQUENCY | 48 | 48 | D Q | 19 | 19 | ANGLE TO | 14 | DAC | DAC_OUT |

TUNING WORD |

|

|

|

| AMPLITUDE |

|

| ||

(FTW) |

|

|

|

|

| CONVERSION |

| DAC_OUTB | |

|

|

|

|

|

|

| |||

fS

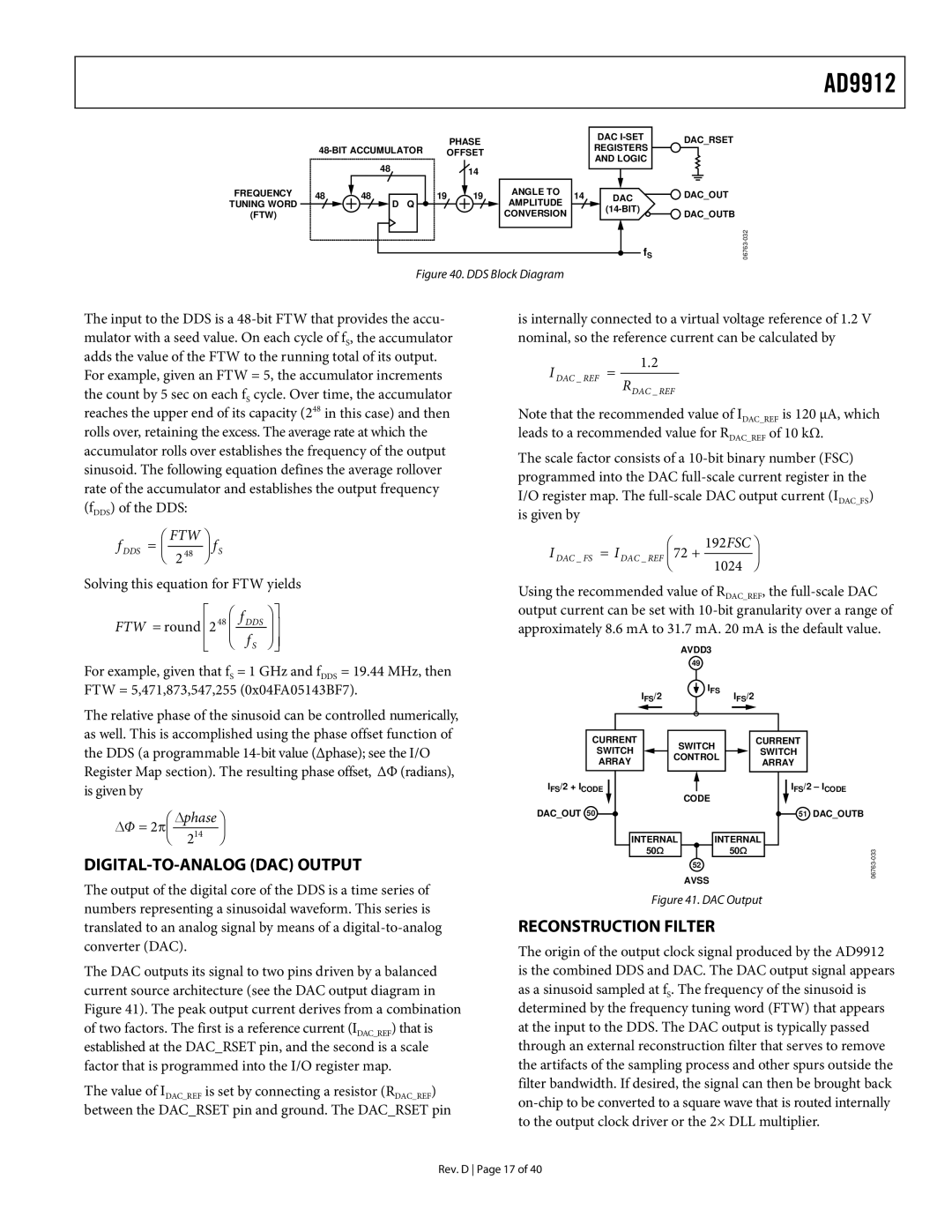

Figure 40. DDS Block Diagram

The input to the DDS is a

For example, given an FTW = 5, the accumulator increments the count by 5 sec on each fS cycle. Over time, the accumulator reaches the upper end of its capacity (248 in this case) and then rolls over, retaining the excess. The average rate at which the accumulator rolls over establishes the frequency of the output sinusoid. The following equation defines the average rollover rate of the accumulator and establishes the output frequency (fDDS) of the DDS:

| FTW | ||

fDDS = |

| fS | |

248 | |||

| | ||

Solving this equation for FTW yields

| 48 | |

|

| |

| | f DDS | |||

FTW = round 2 |

| |

|

| |

|

|

| |||

|

| | f | S | |

|

|

|

| | |

For example, given that fS = 1 GHz and fDDS = 19.44 MHz, then FTW = 5,471,873,547,255 (0x04FA05143BF7).

The relative phase of the sinusoid can be controlled numerically, as well. This is accomplished using the phase offset function of the DDS (a programmable

∆Φ = 2π ∆phase 14 2

DIGITAL-TO-ANALOG (DAC) OUTPUT

The output of the digital core of the DDS is a time series of numbers representing a sinusoidal waveform. This series is translated to an analog signal by means of a

The DAC outputs its signal to two pins driven by a balanced current source architecture (see the DAC output diagram in Figure 41). The peak output current derives from a combination of two factors. The first is a reference current (IDAC_REF) that is established at the DAC_RSET pin, and the second is a scale factor that is programmed into the I/O register map.

The value of IDAC_REF is set by connecting a resistor (RDAC_REF) between the DAC_RSET pin and ground. The DAC_RSET pin

is internally connected to a virtual voltage reference of 1.2 V nominal, so the reference current can be calculated by

I DAC _ REF | = | 1.2 | |

RDAC _ REF | |||

|

|

Note that the recommended value of IDAC_REF is 120 μA, which leads to a recommended value for RDAC_REF of 10 kΩ.

The scale factor consists of a

| |

| 192FSC | |

I DAC _ FS | = I DAC _ REF 72 | + |

| |

| ||||

| |

| 1024 | |

Using the recommended value of RDAC_REF, the

|

|

|

|

|

|

|

|

|

|

|

| AVDD3 |

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| 49 |

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

| IFS/2 |

|

| IFS |

| IFS/2 |

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CURRENT |

|

|

|

|

|

| SWITCH |

|

|

| CURRENT |

|

| |||||||||||

| SWITCH |

|

|

|

|

|

|

|

|

| SWITCH |

|

| ||||||||||||

|

|

|

|

|

| CONTROL |

|

|

|

|

| ||||||||||||||

|

| ARRAY |

|

|

|

|

|

|

|

| ARRAY |

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

IFS/2 + ICODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| IFS/2 – ICODE |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

DAC_OUT 50 |

|

|

|

|

|

|

|

|

|

|

| CODE |

|

|

|

|

|

|

| 51 DAC_OUTB |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

| INTERNAL |

|

|

| INTERNAL |

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

| 50Ω |

|

|

|

| 50Ω |

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

| 52 |

|

|

|

|

|

|

|

|

|

| 06763 | ||

|

|

|

|

|

|

|

|

|

|

|

|

| AVSS |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Figure 41. DAC Output

RECONSTRUCTION FILTER

The origin of the output clock signal produced by the AD9912 is the combined DDS and DAC. The DAC output signal appears as a sinusoid sampled at fS. The frequency of the sinusoid is determined by the frequency tuning word (FTW) that appears at the input to the DDS. The DAC output is typically passed through an external reconstruction filter that serves to remove the artifacts of the sampling process and other spurs outside the filter bandwidth. If desired, the signal can then be brought back

Rev. D Page 17 of 40