PSoC™ Mixed Signal Array | Final Data Sheet |

|

|

CY8C22113 and CY8C22213

Features

■Powerful Harvard Architecture Processor

❐M8C Processor Speeds to 24 MHz

❐Low Power at High Speed

❐3.0 to 5.25 V Operating Voltage

❐Industrial Temperature Range:

■Advanced Peripherals (PSoC Blocks)

❐3

-Up to

-Up to

-Programmable Gain Amplifiers

-Programmable Filters and Comparators

❐4 Digital PSoC Blocks Provide:

-8- to

-CRC and PRS Modules

-

-SPI Masters or Slaves

-Connectable to all GPIO Pins

❐Complex Peripherals by Combining Blocks

■Precision, Programmable Clocking

❐Internal ±2.5% 24/48 MHz Oscillator

❐

❐Optional External Oscillator, up to 24 MHz

❐Internal Oscillator for Watchdog and Sleep

■Flexible On-Chip Memory

❐2K Bytes Flash Program Storage 50,000 Erase/Write Cycles

❐256 Bytes SRAM Data Storage

❐

❐Partial Flash Updates

❐Flexible Protection Modes

❐EEPROM Emulation in Flash

■Programmable Pin Configurations

❐25 mA Sink on all GPIO

❐Pull up, Pull down, High Z, Strong, or Open Drain Drive Modes on all GPIO

❐Up to 8 Analog Inputs on GPIO

❐One 30 mA Analog Outputs on GPIO

❐Configurable Interrupt on all GPIO

■Additional System Resources

❐I2C Slave, Master, and

❐Watchdog and Sleep Timers

❐

❐Integrated Supervisory Circuit

❐

■Complete Development Tools

❐Free Development Software (PSoC™ Designer)

❐

❐Full Speed Emulation

❐Complex Breakpoint Structure

❐128K Bytes Trace Memory

|

| Port 1 | Port 0 Analog |

|

|

| Drivers |

PSoC CORE |

|

|

|

SYSTEM BUS |

|

|

|

Global Digital Interconnect | Global Analog Interconnect | ||

|

| ||

SRAM | SROM | Flash 2K |

|

256 Bytes |

| ||

|

|

| |

Interrupt | CPU Core (M8C) | Sleep and | |

|

| Watchdog | |

Controller |

|

| |

|

|

| |

| Multiple Clock Sources |

| |

(Includes IMO, ILO, PLL, and ECO) | |||

DIGITAL SYSTEM | ANALOG SYSTEM | ||

|

| Analog | Analog |

Digital |

| Ref | |

| Block | ||

Block Array |

| ||

Array |

| ||

|

|

| |

(1 Row, | (1 Column, | Analog | ||||

4 Blocks) | ||||||

3 Blocks) |

|

| Input | |||

|

|

| ||||

|

|

|

|

| Muxing | |

|

|

|

|

|

| |

|

|

|

|

|

| |

Digital |

|

|

|

|

| POR and LVD |

| Internal | ||

| Decimator |

| I2C |

|

|

|

|

| Voltage | |

Clocks |

|

|

| System Resets |

| |||||

|

|

|

|

|

| Ref. | ||||

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

SYSTEM RESOURCES

PSoC™ Functional Overview

The PSoC™ family consists of many Mixed Signal Array with

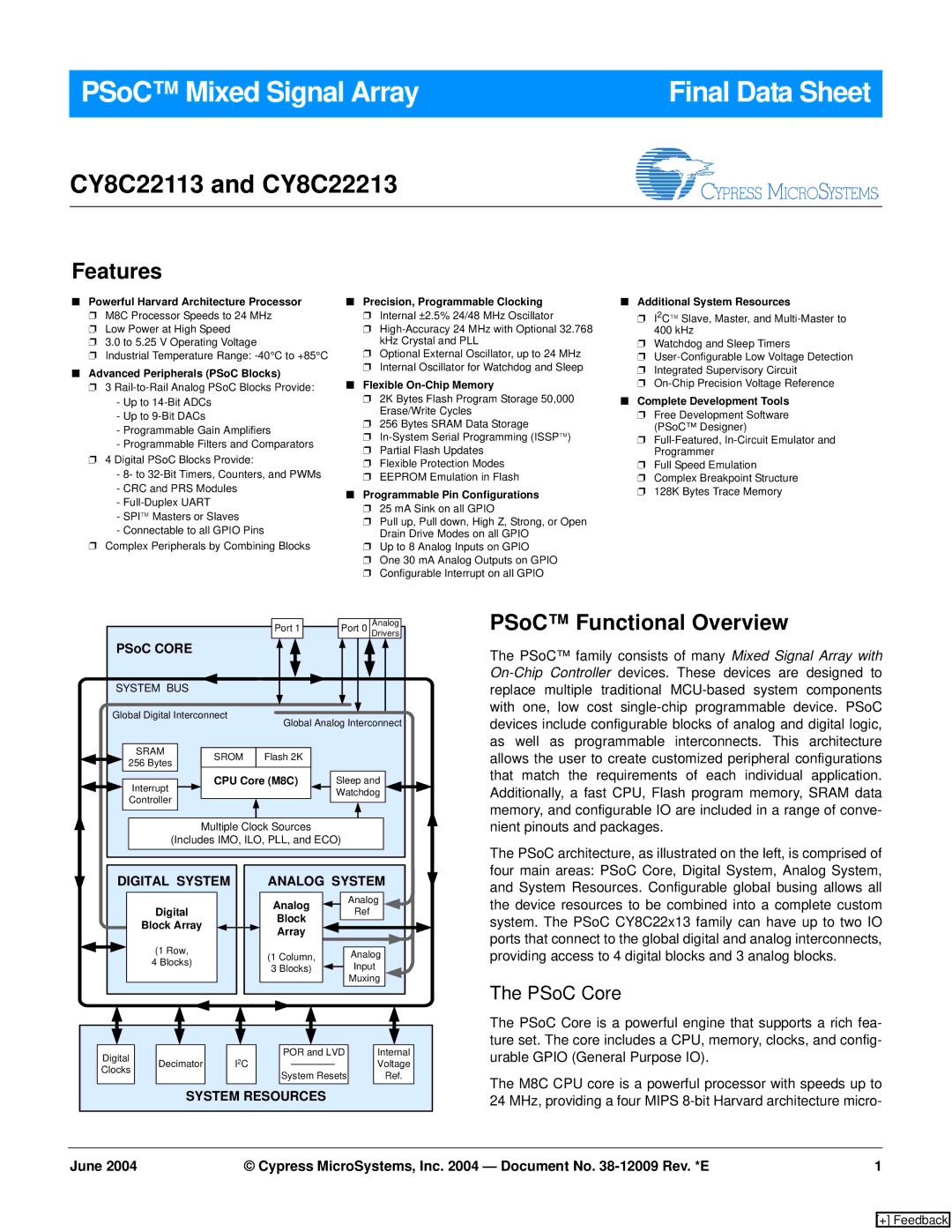

The PSoC architecture, as illustrated on the left, is comprised of four main areas: PSoC Core, Digital System, Analog System, and System Resources. Configurable global busing allows all the device resources to be combined into a complete custom system. The PSoC CY8C22x13 family can have up to two IO ports that connect to the global digital and analog interconnects, providing access to 4 digital blocks and 3 analog blocks.

The PSoC Core

The PSoC Core is a powerful engine that supports a rich fea- ture set. The core includes a CPU, memory, clocks, and config- urable GPIO (General Purpose IO).

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a four MIPS

June 2004 | © Cypress MicroSystems, Inc. 2004 — Document No. | 1 |

[+] Feedback