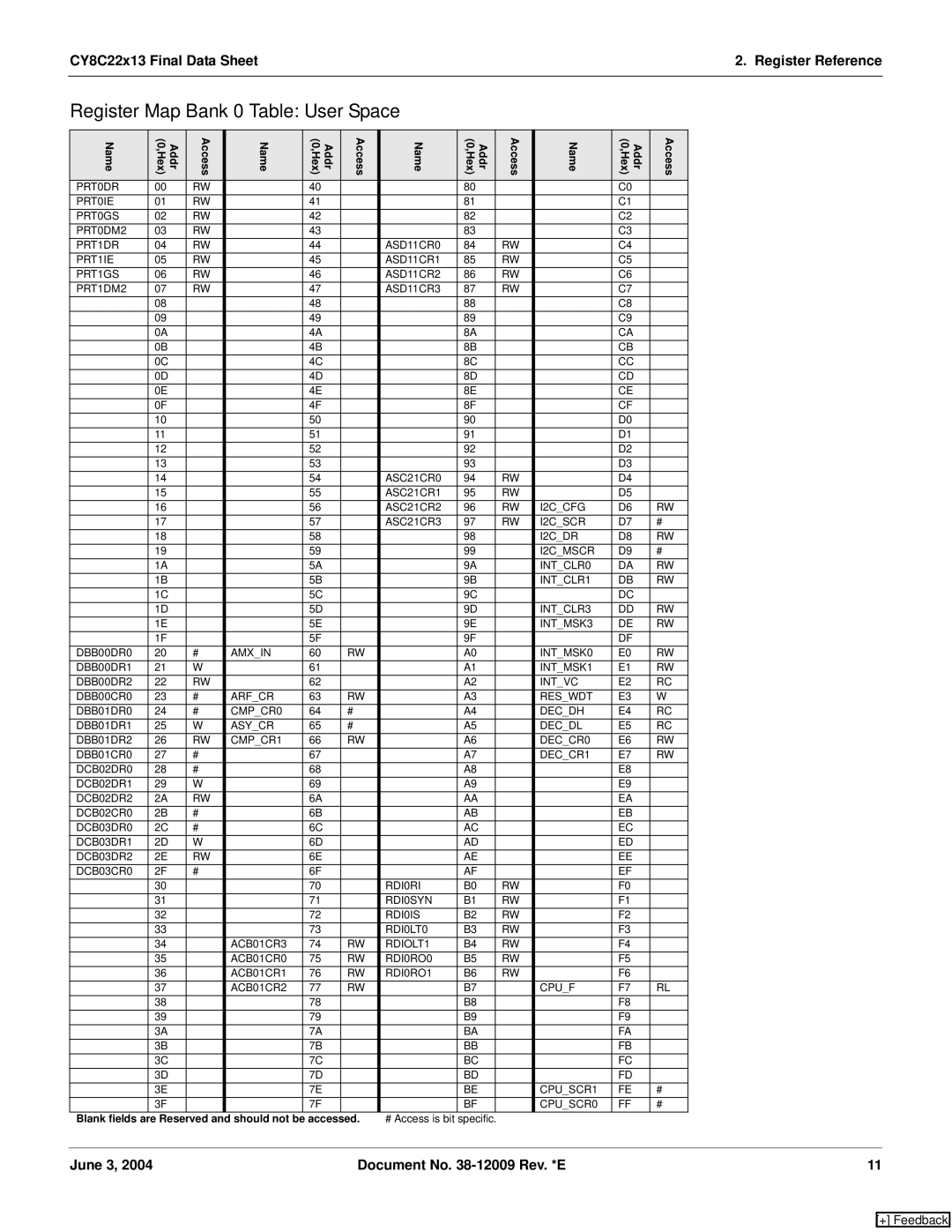

CY8C22x13 Final Data Sheet2. Register Reference

Register Map Bank 0 Table: User Space

Name | Addr (0,Hex) | Access | Name | Addr (0,Hex) | Access | Name | Addr (0,Hex) |

| Access | Name | Addr (0,Hex) | Access |

PRT0DR | 00 | RW |

| 40 |

|

| 80 |

|

|

| C0 |

|

PRT0IE | 01 | RW |

| 41 |

|

| 81 |

|

|

| C1 |

|

PRT0GS | 02 | RW |

| 42 |

|

| 82 |

|

|

| C2 |

|

PRT0DM2 | 03 | RW |

| 43 |

|

| 83 |

|

|

| C3 |

|

PRT1DR | 04 | RW |

| 44 |

| ASD11CR0 | 84 |

| RW |

| C4 |

|

PRT1IE | 05 | RW |

| 45 |

| ASD11CR1 | 85 |

| RW |

| C5 |

|

PRT1GS | 06 | RW |

| 46 |

| ASD11CR2 | 86 |

| RW |

| C6 |

|

PRT1DM2 | 07 | RW |

| 47 |

| ASD11CR3 | 87 |

| RW |

| C7 |

|

| 08 |

|

| 48 |

|

| 88 |

|

|

| C8 |

|

| 09 |

|

| 49 |

|

| 89 |

|

|

| C9 |

|

| 0A |

|

| 4A |

|

| 8A |

|

|

| CA |

|

| 0B |

|

| 4B |

|

| 8B |

|

|

| CB |

|

| 0C |

|

| 4C |

|

| 8C |

|

|

| CC |

|

| 0D |

|

| 4D |

|

| 8D |

|

|

| CD |

|

| 0E |

|

| 4E |

|

| 8E |

|

|

| CE |

|

| 0F |

|

| 4F |

|

| 8F |

|

|

| CF |

|

| 10 |

|

| 50 |

|

| 90 |

|

|

| D0 |

|

| 11 |

|

| 51 |

|

| 91 |

|

|

| D1 |

|

| 12 |

|

| 52 |

|

| 92 |

|

|

| D2 |

|

| 13 |

|

| 53 |

|

| 93 |

|

|

| D3 |

|

| 14 |

|

| 54 |

| ASC21CR0 | 94 |

| RW |

| D4 |

|

| 15 |

|

| 55 |

| ASC21CR1 | 95 |

| RW |

| D5 |

|

| 16 |

|

| 56 |

| ASC21CR2 | 96 |

| RW | I2C_CFG | D6 | RW |

| 17 |

|

| 57 |

| ASC21CR3 | 97 |

| RW | I2C_SCR | D7 | # |

| 18 |

|

| 58 |

|

| 98 |

|

| I2C_DR | D8 | RW |

| 19 |

|

| 59 |

|

| 99 |

|

| I2C_MSCR | D9 | # |

| 1A |

|

| 5A |

|

| 9A |

|

| INT_CLR0 | DA | RW |

| 1B |

|

| 5B |

|

| 9B |

|

| INT_CLR1 | DB | RW |

| 1C |

|

| 5C |

|

| 9C |

|

|

| DC |

|

| 1D |

|

| 5D |

|

| 9D |

|

| INT_CLR3 | DD | RW |

| 1E |

|

| 5E |

|

| 9E |

|

| INT_MSK3 | DE | RW |

| 1F |

|

| 5F |

|

| 9F |

|

|

| DF |

|

DBB00DR0 | 20 | # | AMX_IN | 60 | RW |

| A0 |

|

| INT_MSK0 | E0 | RW |

DBB00DR1 | 21 | W |

| 61 |

|

| A1 |

|

| INT_MSK1 | E1 | RW |

DBB00DR2 | 22 | RW |

| 62 |

|

| A2 |

|

| INT_VC | E2 | RC |

DBB00CR0 | 23 | # | ARF_CR | 63 | RW |

| A3 |

|

| RES_WDT | E3 | W |

DBB01DR0 | 24 | # | CMP_CR0 | 64 | # |

| A4 |

|

| DEC_DH | E4 | RC |

DBB01DR1 | 25 | W | ASY_CR | 65 | # |

| A5 |

|

| DEC_DL | E5 | RC |

DBB01DR2 | 26 | RW | CMP_CR1 | 66 | RW |

| A6 |

|

| DEC_CR0 | E6 | RW |

DBB01CR0 | 27 | # |

| 67 |

|

| A7 |

|

| DEC_CR1 | E7 | RW |

DCB02DR0 | 28 | # |

| 68 |

|

| A8 |

|

|

| E8 |

|

DCB02DR1 | 29 | W |

| 69 |

|

| A9 |

|

|

| E9 |

|

DCB02DR2 | 2A | RW |

| 6A |

|

| AA |

|

|

| EA |

|

DCB02CR0 | 2B | # |

| 6B |

|

| AB |

|

|

| EB |

|

DCB03DR0 | 2C | # |

| 6C |

|

| AC |

|

|

| EC |

|

DCB03DR1 | 2D | W |

| 6D |

|

| AD |

|

|

| ED |

|

DCB03DR2 | 2E | RW |

| 6E |

|

| AE |

|

|

| EE |

|

DCB03CR0 | 2F | # |

| 6F |

|

| AF |

|

|

| EF |

|

| 30 |

|

| 70 |

| RDI0RI | B0 |

| RW |

| F0 |

|

| 31 |

|

| 71 |

| RDI0SYN | B1 |

| RW |

| F1 |

|

| 32 |

|

| 72 |

| RDI0IS | B2 |

| RW |

| F2 |

|

| 33 |

|

| 73 |

| RDI0LT0 | B3 |

| RW |

| F3 |

|

| 34 |

| ACB01CR3 | 74 | RW | RDIOLT1 | B4 |

| RW |

| F4 |

|

| 35 |

| ACB01CR0 | 75 | RW | RDI0RO0 | B5 |

| RW |

| F5 |

|

| 36 |

| ACB01CR1 | 76 | RW | RDI0RO1 | B6 |

| RW |

| F6 |

|

| 37 |

| ACB01CR2 | 77 | RW |

| B7 |

|

| CPU_F | F7 | RL |

| 38 |

|

| 78 |

|

| B8 |

|

|

| F8 |

|

| 39 |

|

| 79 |

|

| B9 |

|

|

| F9 |

|

| 3A |

|

| 7A |

|

| BA |

|

|

| FA |

|

| 3B |

|

| 7B |

|

| BB |

|

|

| FB |

|

| 3C |

|

| 7C |

|

| BC |

|

|

| FC |

|

| 3D |

|

| 7D |

|

| BD |

|

|

| FD |

|

| 3E |

|

| 7E |

|

| BE |

|

| CPU_SCR1 | FE | # |

| 3F |

|

| 7F |

|

| BF |

|

| CPU_SCR0 | FF | # |

Blank fields are Reserved and should not be accessed. | # Access is bit specific. |

|

|

|

| |||||||

June 3, 2004 | Document No. | 11 |

[+] Feedback