CY8C22x13 Final Data Sheet | 3. Electrical Specifications |

|

|

3.4AC Electrical Characteristics

3.4.1AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and

Table 3-15. AC Chip-Level Specifications

| Symbol | Description | Min | Typ | Max | Units | Notes | |

FIMO | Internal Main Oscillator Frequency | 23.4 | 24 | 24.6a | MHz | Trimmed. Utilizing factory trim values. | ||

FCPU1 | CPU Frequency (5V Nominal) | 0.93 | 24 | 24.6a,b | MHz |

| ||

FCPU2 | CPU Frequency (3.3V Nominal) | 0.93 | 12 | 12.3b,c | MHz |

| ||

F48M | Digital PSoC Block Frequency | 0 | 48 | 49.2a,b,d | MHz | Refer to the AC Digital Block Specifications | ||

|

|

|

|

|

|

|

| below. |

F24M | Digital PSoC Block Frequency | 0 | 24 | 24.6b,e,d | MHz |

| ||

F32K1 | Internal Low Speed Oscillator Frequency | 15 | 32 | 64 | kHz |

| ||

F32K2 | External Crystal Oscillator | – | 32.768 | – | kHz | Accuracy is capacitor and crystal dependent. | ||

|

|

|

|

|

|

|

| 50% duty cycle. |

|

|

|

|

|

|

|

|

|

FPLL | PLL Frequency | – | 23.986 | – | MHz | Is a multiple (x732) of crystal frequency. | ||

Jitter24M2 | 24 MHz Period Jitter (PLL) | – | – | 600 | ps |

| ||

|

|

|

|

|

|

|

|

|

TPLLSLEW | PLL Lock Time | 0.5 | – | 10 | ms |

| ||

TPLLSLEWS- | PLL Lock Time for Low Gain Setting | 0.5 | – | 50 | ms |

| ||

LOW |

|

|

|

|

|

|

| |

TOS | External Crystal Oscillator Startup to 1% | – | 1700 | 2620 | ms |

| ||

TOSACC | External Crystal Oscillator Startup to 100 ppm | – | 2800 | 3800f | ms |

| ||

Jitter32k | 32 kHz Period Jitter | – | 100 |

| ns |

| ||

|

|

|

|

|

|

|

|

|

TXRST | External Reset Pulse Width | 10 | – | – | ∝s |

| ||

DC24M | 24 MHz Duty Cycle | 40 | 50 | 60 | % |

| ||

|

|

|

|

|

|

|

|

|

Step24M | 24 MHz Trim Step Size | – | 50 | – | kHz |

| ||

|

|

|

|

|

|

|

|

|

Fout48M | 48 MHz Output Frequency | 46.8 | 48.0 | 49.2a,c | MHz | Trimmed. Utilizing factory trim values. | ||

Jitter24M1 | 24 MHz Period Jitter (IMO) | – | 600 |

| ps |

| ||

|

|

|

|

|

|

|

|

|

FMAX | Maximum frequency of signal on row input or row output. | – | – | 12.3 | MHz |

| ||

TRAMP | Supply Ramp Time | 0 | – | – | ∝s |

| ||

|

|

|

|

|

|

|

|

|

a.4.75V < Vdd < 5.25V.

b.Accuracy derived from Internal Main Oscillator with appropriate trim for Vdd range.

c.3.0V < Vdd < 3.6V. See Application Note AN2012 “Adjusting PSoC Microcontroller Trims for Dual

d.See the individual user module data sheets for information on maximum frequencies for user modules.

e.3.0V < 5.25V.

f.The crystal oscillator frequency is within 100 ppm of its final value by the end of the Tosacc period. Correct operation assumes a properly loaded 1 uW maximum drive level 32.768 kHz crystal. 3.0V ≤ Vdd ≤ 5.5V,

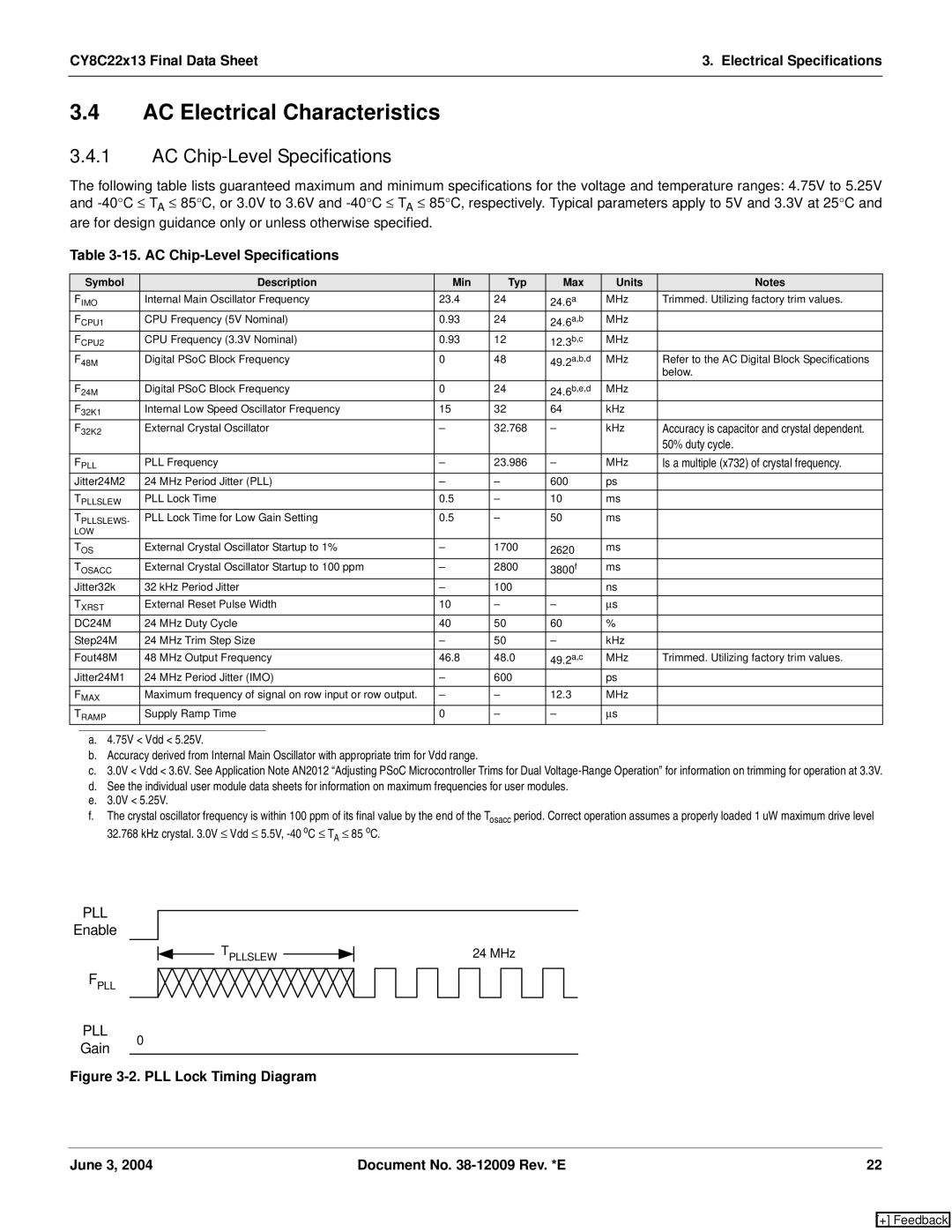

PLL

Enable

TPLLSLEW |

| 24 MHz |

|

FPLL

PLL

0

Gain

Figure 3-2. PLL Lock Timing Diagram

June 3, 2004 | Document No. | 22 |

[+] Feedback