CY8C24123A specifications

The Cypress CY8C24123A is a prominent member of the PSoC (Programmable System-on-Chip) family, which integrates a microcontroller with programmable analog and digital components on a single chip. Designed for low-power applications, the CY8C24123A offers a compelling mix of features and technologies that make it a popular choice for embedded system developers.One of the standout features of the CY8C24123A is its low power consumption, which allows it to extend battery life in portable applications. It operates at a voltage range of 1.71V to 5.5V, making it versatile for various power supply options. This device is equipped with a 24 MHz CPU that efficiently executes tasks while keeping energy usage minimal.

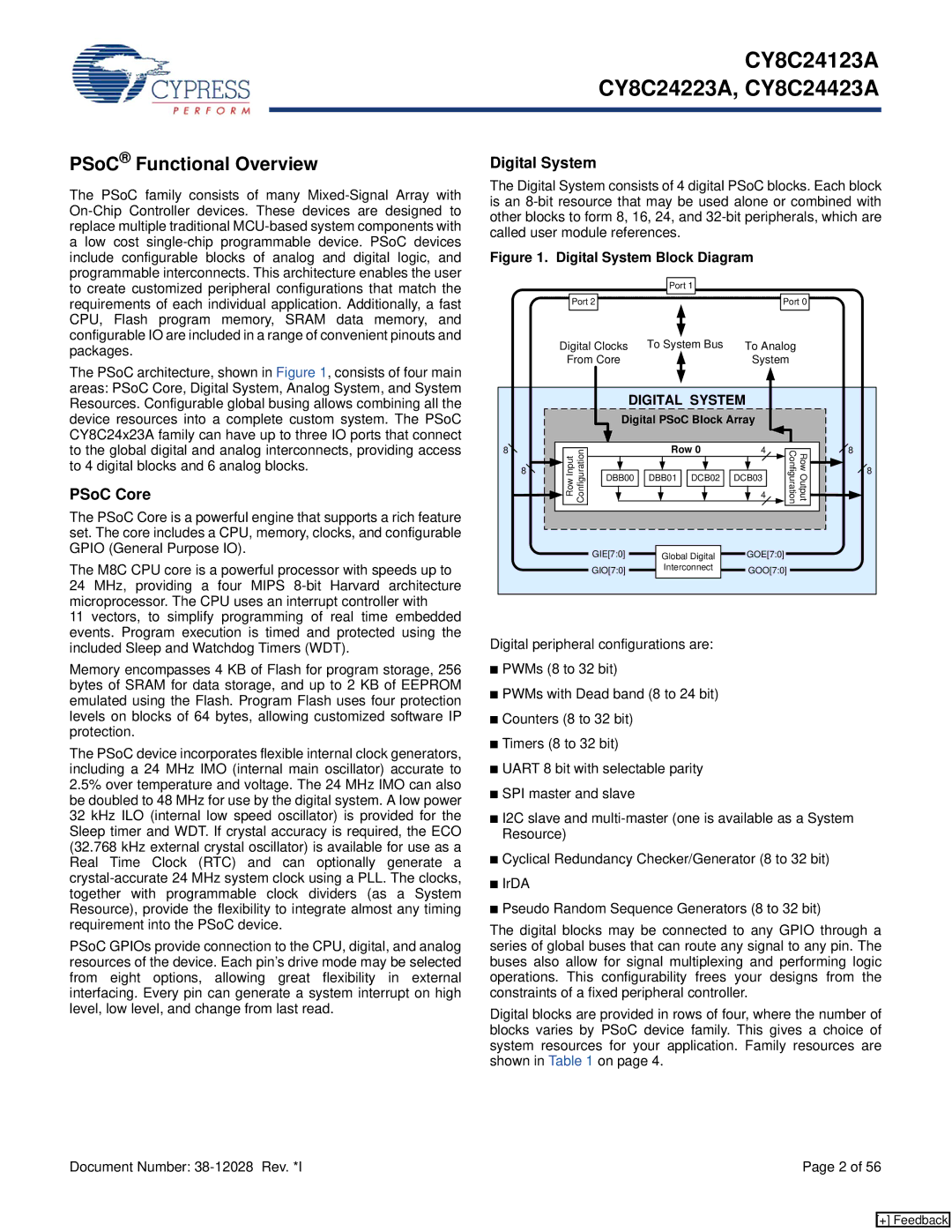

The chip boasts a rich set of programmable peripherals, including analog components such as operational amplifiers, comparators, and DACs, enabling designers to create custom signal processing pathways. These features are complemented by a variety of digital peripherals, like timers, UART, I2C, and SPI interfaces, which facilitate communication with other devices and microcontrollers. The integration of these components reduces the need for external components, leading to a more compact design and lower overall system costs.

Moreover, the CY8C24123A includes Flash memory (up to 2 KB) and SRAM (256 bytes), providing ample storage for application code and data. This Flash memory is reprogrammable, enabling developers to update their applications easily without needing to replace the chip.

Another defining characteristic of the CY8C24123A is its programmability. The device can be configured and programmed using the Cypress PSoC Designer software, which allows developers to design and simulate their applications in a user-friendly environment. The combination of hardware-based flexibility and software configuration provides a robust platform for creating custom solutions tailored to specific application requirements.

Overall, the Cypress CY8C24123A stands out for its balance of performance, programmability, and power efficiency. Its integration of programmable analog and digital blocks makes it suitable for a wide range of applications, including industrial control, consumer electronics, and automotive systems. The ability to customize the chip's functionality further boosts its appeal, making it an excellent choice for developers seeking a versatile and efficient solution for their embedded projects.