CYD01S36V

CYD02S36V/36VA/CYD04S36V

CYD09S36V/CYD18S36V

FLEx36™ 3.3V 32K/64K/128K/256K/512 x 36 Synchronous

Features

■True

■Synchronous pipelined operation

■Family of

■Pipelined output mode allows fast operation

■0.18 micron CMOS for optimum speed and power

■High speed clock to data access

■3.3V low power

❐Active as low as 225 mA (typ.)

❐Standby as low as 55 mA (typ.)

■Mailbox function for message passing

■Global master reset

■Separate byte enables on both ports

■Commercial and industrial temperature ranges

■IEEE

■256 Ball FBGA

■Counter wrap around control

❐Internal mask register controls counter

❐

❐Memory block retransmit operation

■Counter readback on address lines

■Mask register readback on address lines

■Dual Chip Enables on both ports for easy depth expansion

■Seamless migration to

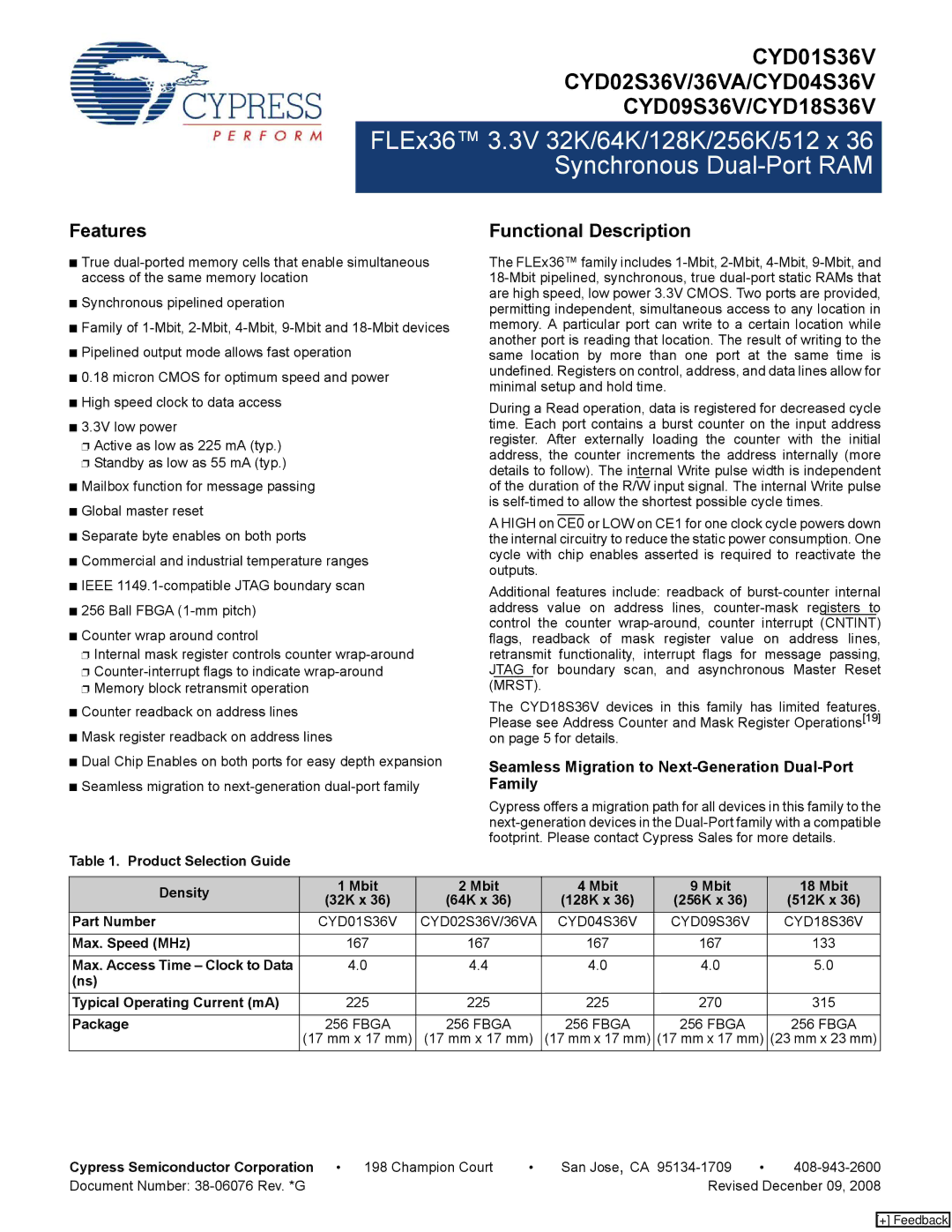

Table 1. Product Selection Guide

Functional Description

The FLEx36™ family includes

During a Read operation, data is registered for decreased cycle time. Each port contains a burst counter on the input address register. After externally loading the counter with the initial address, the counter increments the address internally (more details to follow). The internal Write pulse width is independent of the duration of the R/W input signal. The internal Write pulse is

A HIGH on CE0 or LOW on CE1 for one clock cycle powers down the internal circuitry to reduce the static power consumption. One cycle with chip enables asserted is required to reactivate the outputs.

Additional features include: readback of

The CYD18S36V devices in this family has limited features. Please see Address Counter and Mask Register Operations[19] on page 5 for details.

Seamless Migration to Next-Generation Dual-Port Family

Cypress offers a migration path for all devices in this family to the

Density | 1 Mbit | 2 Mbit | 4 Mbit | 9 Mbit | 18 Mbit | |

(32K x 36) | (64K x 36) | (128K x 36) | (256K x 36) | (512K x 36) | ||

| ||||||

Part Number | CYD01S36V | CYD02S36V/36VA | CYD04S36V | CYD09S36V | CYD18S36V | |

Max. Speed (MHz) | 167 | 167 | 167 | 167 | 133 | |

|

|

|

|

|

| |

Max. Access Time – Clock to Data | 4.0 | 4.4 | 4.0 | 4.0 | 5.0 | |

(ns) |

|

|

|

|

| |

Typical Operating Current (mA) | 225 | 225 | 225 | 270 | 315 | |

|

|

|

|

|

| |

Package | 256 FBGA | 256 FBGA | 256 FBGA | 256 FBGA | 256 FBGA | |

| (17 mm x 17 mm) | (17 mm x 17 mm) | (17 mm x 17 mm) | (17 mm x 17 mm) | (23 mm x 23 mm) |

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document Number: |

| Revised Decenber 09, 2008 | ||

[+] Feedback