CYD01S36V

CYD02S36V/36VA/CYD04S36V

CYD09S36V/CYD18S36V

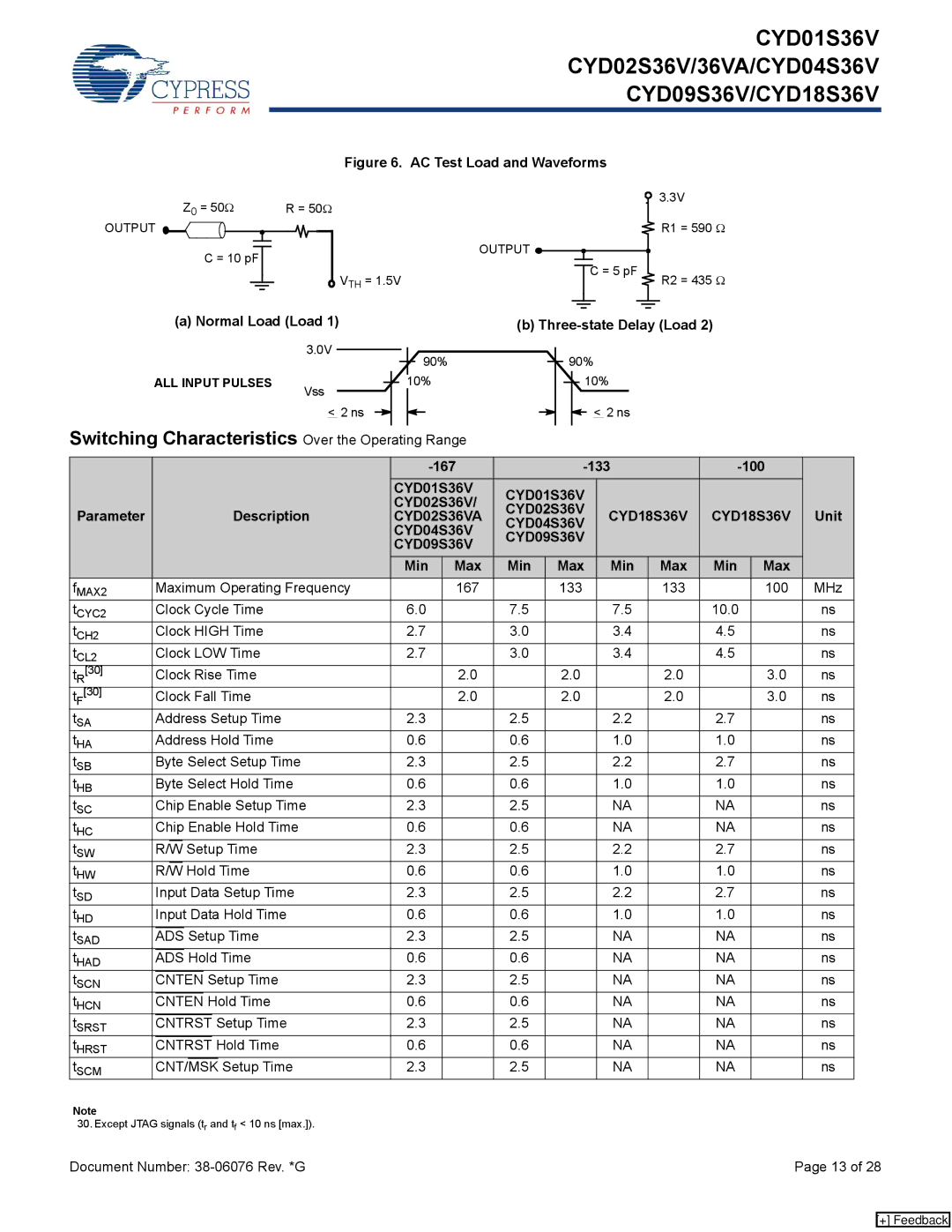

Figure 6. AC Test Load and Waveforms

Z0 = 50Ω

OUTPUT

C = 10 pF

R = 50Ω

OUTPUT ![]()

![]()

![]()

3.3V

R1 = 590 Ω

![]() VTH = 1.5V

VTH = 1.5V

C = 5 pF

R2 = 435 Ω

(a) Normal Load (Load 1) | (b) |

3.0V

90%

ALL INPUT PULSES |

|

|

|

|

|

|

| |||

Vss |

|

|

|

|

| 10% | ||||

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

| |||||||

| < 2 ns |

|

|

|

|

|

| |||

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

Switching Characteristics Over the Operating Range

90%

10%

< 2 ns

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| CYD01S36V | CYD01S36V |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| CYD02S36V/ |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| CYD02S36V |

|

|

|

|

| |||

| Parameter |

|

|

|

|

|

|

|

|

| Description | CYD02S36VA | CYD18S36V | CYD18S36V | Unit | |||||

|

|

|

|

|

|

|

|

|

| CYD04S36V | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| CYD04S36V |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| CYD09S36V |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| CYD09S36V |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| Min | Max | Min | Max | Min | Max | Min | Max |

|

fMAX2 |

| Maximum Operating Frequency |

| 167 |

| 133 |

| 133 |

| 100 | MHz | |||||||||

tCYC2 |

| Clock Cycle Time | 6.0 |

| 7.5 |

| 7.5 |

| 10.0 |

| ns | |||||||||

tCH2 |

| Clock HIGH Time | 2.7 |

| 3.0 |

| 3.4 |

| 4.5 |

| ns | |||||||||

tCL2 |

| Clock LOW Time | 2.7 |

| 3.0 |

| 3.4 |

| 4.5 |

| ns | |||||||||

t | [30] |

| Clock Rise Time |

| 2.0 |

| 2.0 |

| 2.0 |

| 3.0 | ns | ||||||||

| R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t | [30] |

| Clock Fall Time |

| 2.0 |

| 2.0 |

| 2.0 |

| 3.0 | ns | ||||||||

| F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSA |

| Address Setup Time | 2.3 |

| 2.5 |

| 2.2 |

| 2.7 |

| ns | |||||||||

tHA |

| Address Hold Time | 0.6 |

| 0.6 |

| 1.0 |

| 1.0 |

| ns | |||||||||

tSB |

| Byte Select Setup Time | 2.3 |

| 2.5 |

| 2.2 |

| 2.7 |

| ns | |||||||||

tHB |

| Byte Select Hold Time | 0.6 |

| 0.6 |

| 1.0 |

| 1.0 |

| ns | |||||||||

tSC |

| Chip Enable Setup Time | 2.3 |

| 2.5 |

| NA |

| NA |

| ns | |||||||||

tHC |

| Chip Enable Hold Time | 0.6 |

| 0.6 |

| NA |

| NA |

| ns | |||||||||

tSW |

| R/W |

| Setup Time | 2.3 |

| 2.5 |

| 2.2 |

| 2.7 |

| ns | |||||||

tHW |

| R/W |

| Hold Time | 0.6 |

| 0.6 |

| 1.0 |

| 1.0 |

| ns | |||||||

tSD |

| Input Data Setup Time | 2.3 |

| 2.5 |

| 2.2 |

| 2.7 |

| ns | |||||||||

tHD |

| Input Data Hold Time | 0.6 |

| 0.6 |

| 1.0 |

| 1.0 |

| ns | |||||||||

tSAD |

| ADS |

| Setup Time | 2.3 |

| 2.5 |

| NA |

| NA |

| ns | |||||||

tHAD |

| ADS |

| Hold Time | 0.6 |

| 0.6 |

| NA |

| NA |

| ns | |||||||

tSCN |

| CNTEN | Setup Time | 2.3 |

| 2.5 |

| NA |

| NA |

| ns | ||||||||

tHCN |

| CNTEN | Hold Time | 0.6 |

| 0.6 |

| NA |

| NA |

| ns | ||||||||

tSRST |

| CNTRST |

| Setup Time | 2.3 |

| 2.5 |

| NA |

| NA |

| ns | |||||||

tHRST |

| CNTRST | Hold Time | 0.6 |

| 0.6 |

| NA |

| NA |

| ns | ||||||||

tSCM |

| CNT/MSK | Setup Time | 2.3 |

| 2.5 |

| NA |

| NA |

| ns | ||||||||

Note

30. Except JTAG signals (tr and tf < 10 ns [max.]).

Document Number: | Page 13 of 28 |

[+] Feedback