|

|

|

|

|

|

|

|

| CYD01S36V | ||

|

|

|

|

|

|

| CYD02S36V/36VA/CYD04S36V | ||||

|

|

|

|

|

|

| CYD09S36V/CYD18S36V | ||||

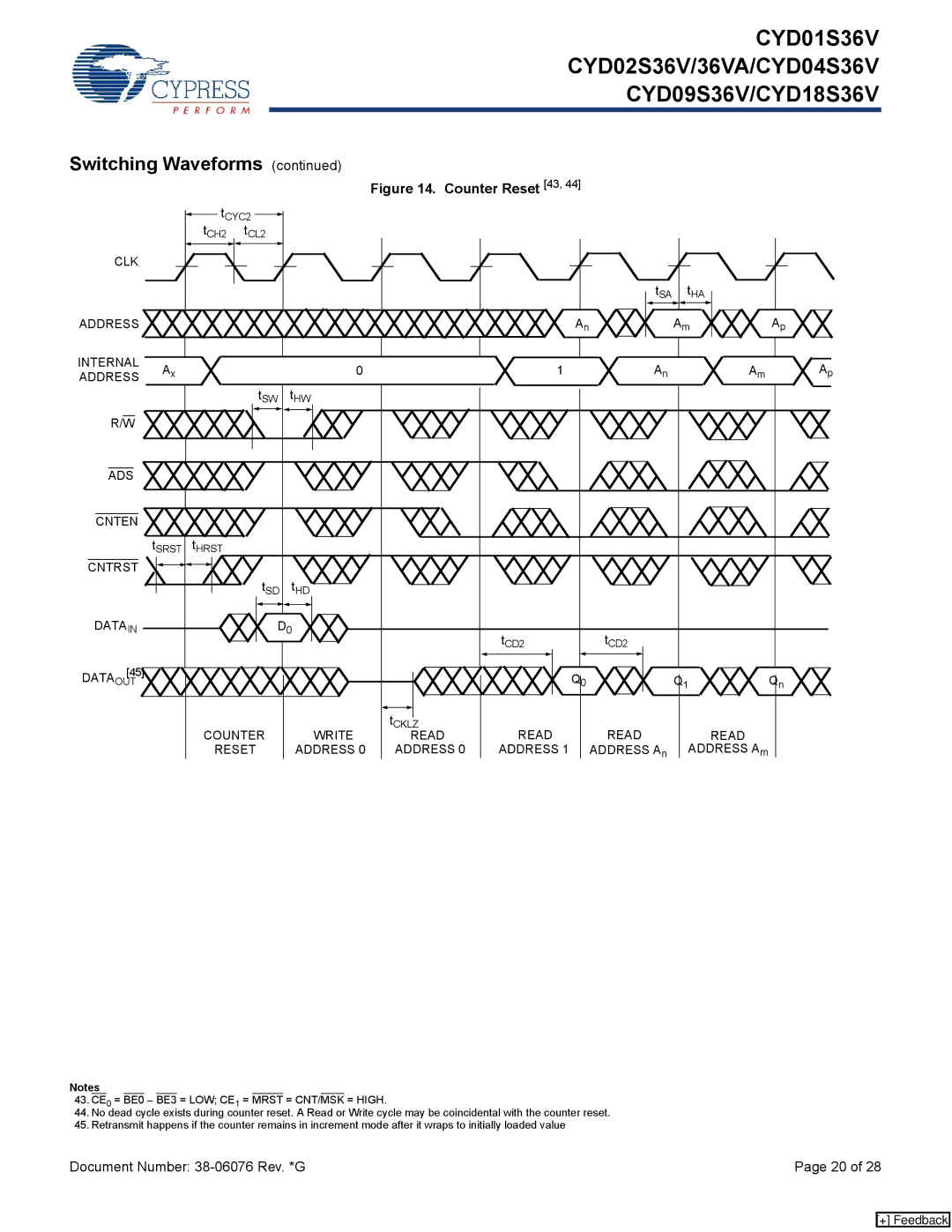

Switching Waveforms (continued) | Figure 14. Counter Reset [43, 44] |

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| ||

|

|

| tCYC2 |

|

|

|

|

|

|

| |

|

|

| tCH2 | tCL2 |

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tSA | tHA |

|

| |

ADDRESS |

|

|

|

|

|

| An |

| Am |

| Ap |

INTERNAL | A | x |

|

| 0 | 1 | A | n | A | m | Ap |

ADDRESS |

|

| |||||||||

|

|

|

|

|

|

|

| ||||

|

|

|

| tSW | tHW |

|

|

|

|

|

|

R/W |

|

|

|

|

|

|

|

|

|

|

|

ADS |

|

|

|

|

|

|

|

|

|

|

|

CNTEN |

|

|

|

|

|

|

|

|

|

|

|

| tSRST | tHRST |

|

|

|

|

|

|

|

| |

CNTRST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tSD | tHD |

|

|

|

|

|

|

DATAIN |

|

|

| D0 | tCD2 | tCD2 |

|

|

|

| |

DATAOUT[45] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Q |

| 0 |

| Q | Q |

| n | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| COUNTER | WRITE | tCKLZ |

|

|

| READ |

|

|

|

| READ |

| READ |

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

| READ |

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

| RESET | ADDRESS 0 | ADDRESS 0 |

| ADDRESS 1 |

|

|

| ADDRESS An | ADDRESS Am |

|

|

| ||||||||||||||||||||

Notes

43.CE0 = BE0 – BE3 = LOW; CE1 = MRST = CNT/MSK = HIGH.

44.No dead cycle exists during counter reset. A Read or Write cycle may be coincidental with the counter reset.

45.Retransmit happens if the counter remains in increment mode after it wraps to initially loaded value

Document Number: | Page 20 of 28 |

[+] Feedback