00809-0100-4696,Rev AA September

Reference Manual

Temperature Transmitter with

Rosemount 848L Discrete Logic

Rosemount 848L

FOUNDATION Fieldbus

SECTION 1 Introduction SECTION 2 Installation

Table of Contents

SECTION 3 Configuration

Rosemount 848L

Reference Data APPENDIX B Product Certifications

SECTION Operation and Maintenance APPENDIX A

APPENDIX C Function Blocks

Rosemount 848L

Motor Control

APPENDIX D Logic Equation Syntax APPENDIX E

APPENDIX F Valve Control

Rosemount 848L

Reference Manual

Rosemount 848L

TOC-4

Section

SAFETY MESSAGES Warnings

Introduction

Rosemount 848L

Transmitter

OVERVIEW

Manual

Rosemount 848L

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

SAFETY MESSAGES Warnings MOUNTING

Installation

Section

Rosemount 848L

Mounting to a Panel with a Junction Box

Mounting to a DIN Rail Without an Enclosure

Rosemount 848L

Reference Manual

Rosemount 848L

Mounting to a 2-InchPipe Stand

Reference Manual

00809-0100-4696,Rev AA September

Power Supply Connections

WIRING

Rosemount 848L

Reference Manual

Surges/Transients

SWITCHES

GROUNDING

Rosemount 848L

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

DISCRETE INPUT WIRING CONFIGURATION

I/O WIRING

DISCRETE OUTPUT WIRING CONFIGURATION

Rosemount 848L

Rosemount 848L

TAGGING

Reference Manual

TRANSMITTER LABEL

INSTALLATION Using Cable Glands

Rosemount 848L

Reference Manual

Rosemount 848L

Using Conduit Entries

Reference Manual

OVERVIEW SAFETY MESSAGES Warnings

Configuration

Section

Rosemount 848L

Rosemount 848L

GENERAL BLOCK INFORMATION Modes

Reference Manual

Rosemount 848L

Link Active Scheduler Block Instantiation

Reference Manual

Capabilities

RESOURCE BLOCK FEATURES and FEATURES SEL

Rosemount 848L

Reference Manual

Rosemount 848L

MAX NOTIFY

Reference Manual

Rosemount 848L

PlantWeb Alarms

Reference Manual

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Rosemount 848L

Alarms I/O TRANSDUCER BLOCK

Reference Manual

Rosemount 848L

LOGIC TRANSDUCER BLOCK

Reference Manual

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Figure 3-1.848L Logic Transmitter Data Flow

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Rosemount 848L

DISCRETE INPUT BLOCKS

Reference Manual

MULTIPLE DISCRETE INPUT BLOCK

DISCRETE OUTPUT BLOCKS

MULTIPLE DISCRETE OUTPUT BLOCK

Rosemount 848L

Reference Manual

Rosemount 848L

FOUNDATION FIELDBUS INFORMATION

Section 4 Operation and Maintenance

SAFETY MESSAGES Warnings

Rosemount 848L

Communication/Power

MAINTENANCE

Resetting the Configuration RESTART

Commissioning

I/O Transducer and Logic Block Troubleshooting

TROUBLESHOOTING

Resource Block

NAMUR Sensors

Reference Manual

Rosemount 848L

Appendix A

SPECIFICATIONS Functional Specifications

Reference Data

Rosemount 848L

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Specification

Physical Specifications Function Blocks

Rosemount 848L

Reference Manual

Rosemount 848L

DIMENSIONAL DRAWINGS

Reference Manual

Rosemount 848L

Figure A-3.Rosemount 848L Wiring Diagram

Reference Manual

00809-0100-4696,Rev AA September

Rosemount 848L

ORDERING INFORMATION

Reference Manual

Reference Manual

Rosemount 848L

APPROVED MANUFACTURING LOCATIONS

Appendix B Product Certifications

EUROPEAN DIRECTIVE INFORMATION HAZARDOUS

LOCATIONS CERTIFICATES North American Approvals

Rosemount 848L

European Approvals

Reference Manual

RESOURCE BLOCK PARAMETERS

Appendix C Function Blocks

Rosemount 848L

Reference Manual

Reference Manual

Rosemount 848L

FREE SPACE

Reference Manual

Rosemount 848L

OUTPUT

Rosemount 848L

ADVISE ENABLE

Reference Manual

Rosemount 848L

I/O TRANSDUCER PARAMETERS

Reference Manual

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

TRANSDUCER TYPE

Reference Manual

Rosemount 848L

OUT 3 TAG

Rosemount 848L

LOGIC TRANSDUCER PARAMETERS

Reference Manual

00809-0100-4696,Rev AA September

Rosemount 848L

DISCRETE INPUT BLOCK

Reference Manual

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Table C-4.Parameters

Rosemount 848L

DISCRETE OUTPUT BLOCK Supported Modes

Reference Manual

Rosemount 848L

MULTIPLE DISCRETE INPUT BLOCKS

Reference Manual

Reference Manual

Rosemount 848L

MULTIPLE DISCRETE OUTPUT BLOCK

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Table C-7.Parameters and

Rosemount 848L

Appendix D Logic Equation Syntax

Reference Manual

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

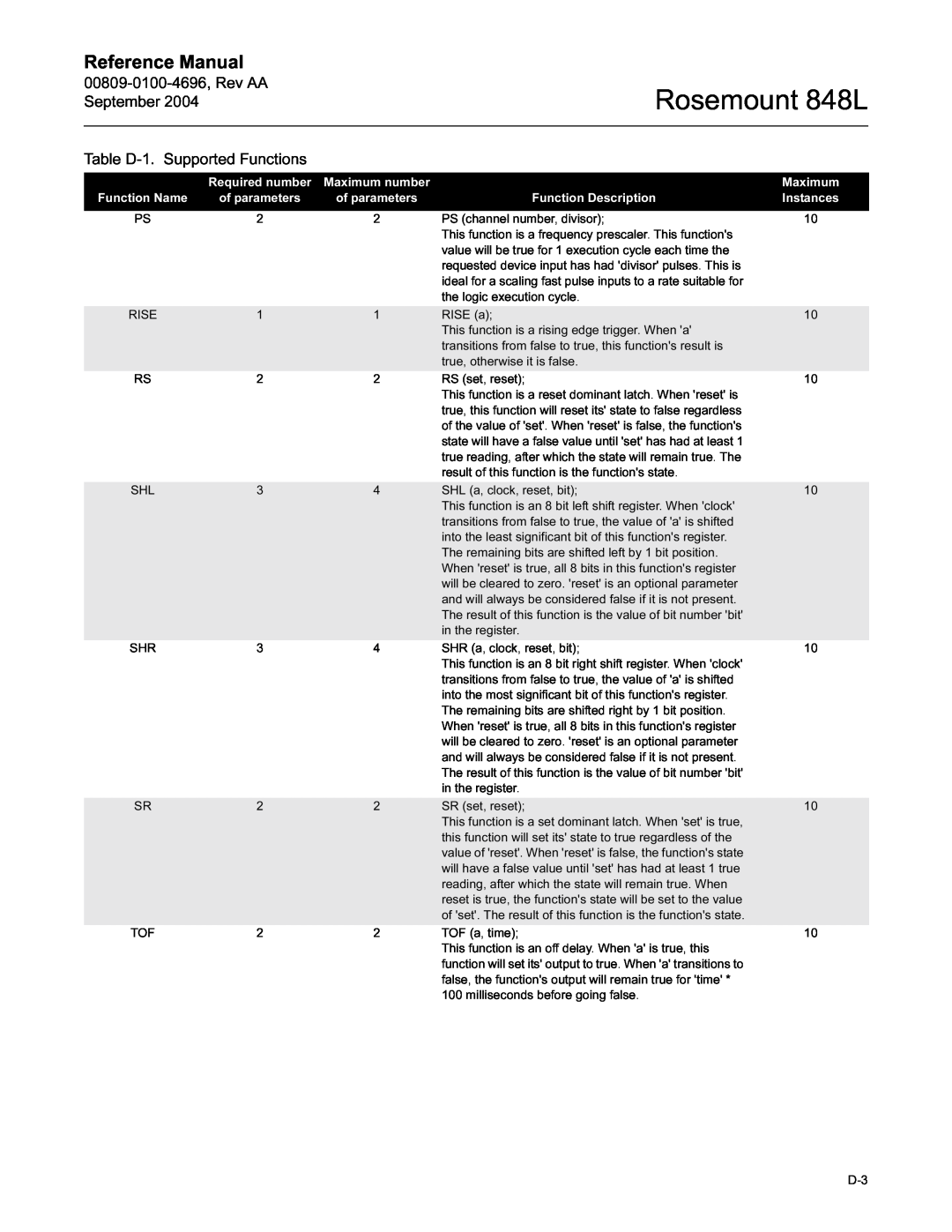

Table D-1.Supported Functions

Reference Manual

Rosemount 848L

PS channel number, divisor

Table D-2.Error Handling

ERROR HANDLING

Rosemount 848L

Reference Manual

Rosemount 848L

EXAMPLES

Reference Manual

Reference Manual

Rosemount 848L

Motor Control

Appendix E

INTRODUCTION TO MOTOR CONTROL

Rosemount 848L

Rosemount 848L

VARIATIONS ON MOTOR CONTROL

Reference Manual

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Rosemount 848L

WRITING 848L EQUATIONS Basic Motor Control

Reference Manual

Rosemount 848L

Interlock Permissive Emergency Shutdown

Reference Manual

Rosemount 848L

Restart Delay

Reference Manual

Rosemount 848L

Maximum Restarts

Reference Manual

Rosemount 848L

Winding Temperature

Reference Manual

Rosemount 848L

Hand-Off-Auto

Reference Manual

Rosemount 848L

Intermediate Stop

Reference Manual

Rosemount 848L

Redundant Motors - Alternate Start

Reference Manual

Rosemount 848L

Redundant Motors - Timed Switch

Reference Manual

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Rosemount 848L

Redundant Motors - Switch on Failure

Reference Manual

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA September

Reference Manual

Rosemount 848L

E-16

Valve Control

Appendix F

INTRODUCTION TO VALVE CONTROL

Rosemount 848L

Rosemount 848L

Alarms Variations on Valve Control

Reference Manual

Rosemount 848L

Boolean Expressions Basic Valve Control

Reference Manual

Output Variations Output with Interlock

Open-Auto-Close Alarm Variations

Rosemount 848L

Reference Manual

Rosemount 848L

Simple Valve Variations Permissive

Reference Manual

Rosemount 848L

Double Block and Bleed

Reference Manual

Rosemount 848L

Motorized Valve Heat Exchange Medium Selection

Reference Manual

Reference Manual

Rosemount 848L

Rosemount 848L

Index

Reference Manual

00809-0100-4696,Rev AA 9/17/04

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA 9/17/04

Reference Manual

Rosemount 848L

00809-0100-4696,Rev AA 9/17/04

Reference Manual

Rosemount 848L

Index-4

Reference Manual

¢00809-0100-4697F¤