|

|

|

|

|

|

| Chapter 2 | Installations | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 100MHz | 66MHz | 4x |

| |

|

| off off off on on off on off |

|

|

|

|

|

|

|

|

|

|

|

| 100MHz | 66MHz | 4.5x |

| |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| |

|

| off off off on on on on off |

|

|

|

|

|

| |

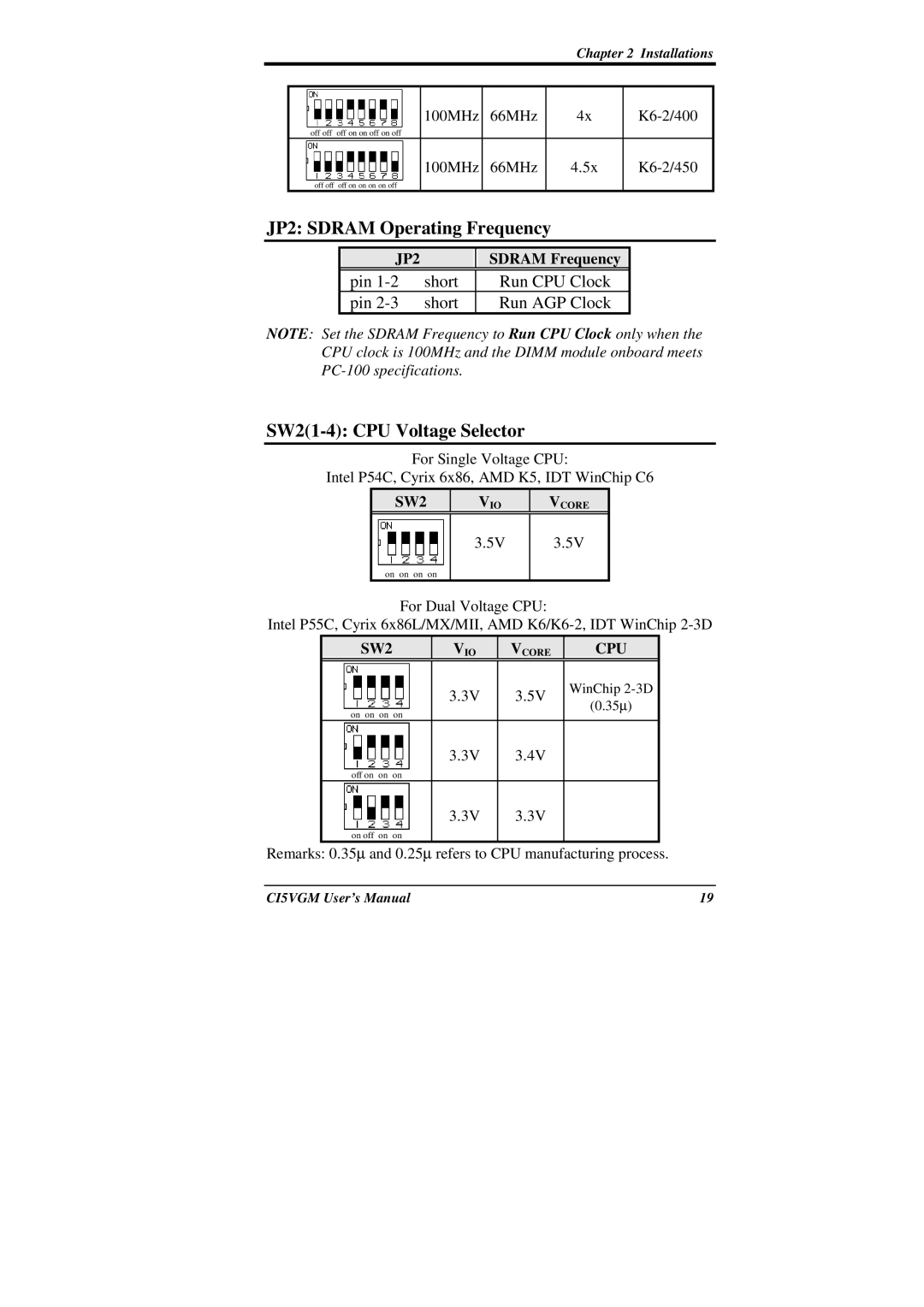

JP2: SDRAM Operating Frequency

JP2 |

|

| SDRAM Frequency |

|

|

|

|

pin | short |

| Run CPU Clock |

pin | short |

| Run AGP Clock |

NOTE: Set the SDRAM Frequency to Run CPU Clock only when the CPU clock is 100MHz and the DIMM module onboard meets

SW2(1-4): CPU Voltage Selector

For Single Voltage CPU:

Intel P54C, Cyrix 6x86, AMD K5, IDT WinChip C6

SW2

VIO

VCORE

3.5V

3.5V

on on on on

For Dual Voltage CPU:

Intel P55C, Cyrix 6x86L/MX/MII, AMD

SW2 | VIO | VCORE | CPU | |

|

|

|

| |

|

|

|

| |

| 3.3V | 3.5V | WinChip | |

| (0.35∝ ) | |||

on on on on |

|

| ||

|

|

| ||

| 3.3V | 3.4V |

| |

off on on on |

|

|

| |

| 3.3V | 3.3V |

| |

on off on on |

|

|

|

Remarks: 0.35∝ and 0.25∝ refers to CPU manufacturing process.

CI5VGM User’s Manual | 19 |