Chapter 3 BIOS Configuration

Chipset Features Setup

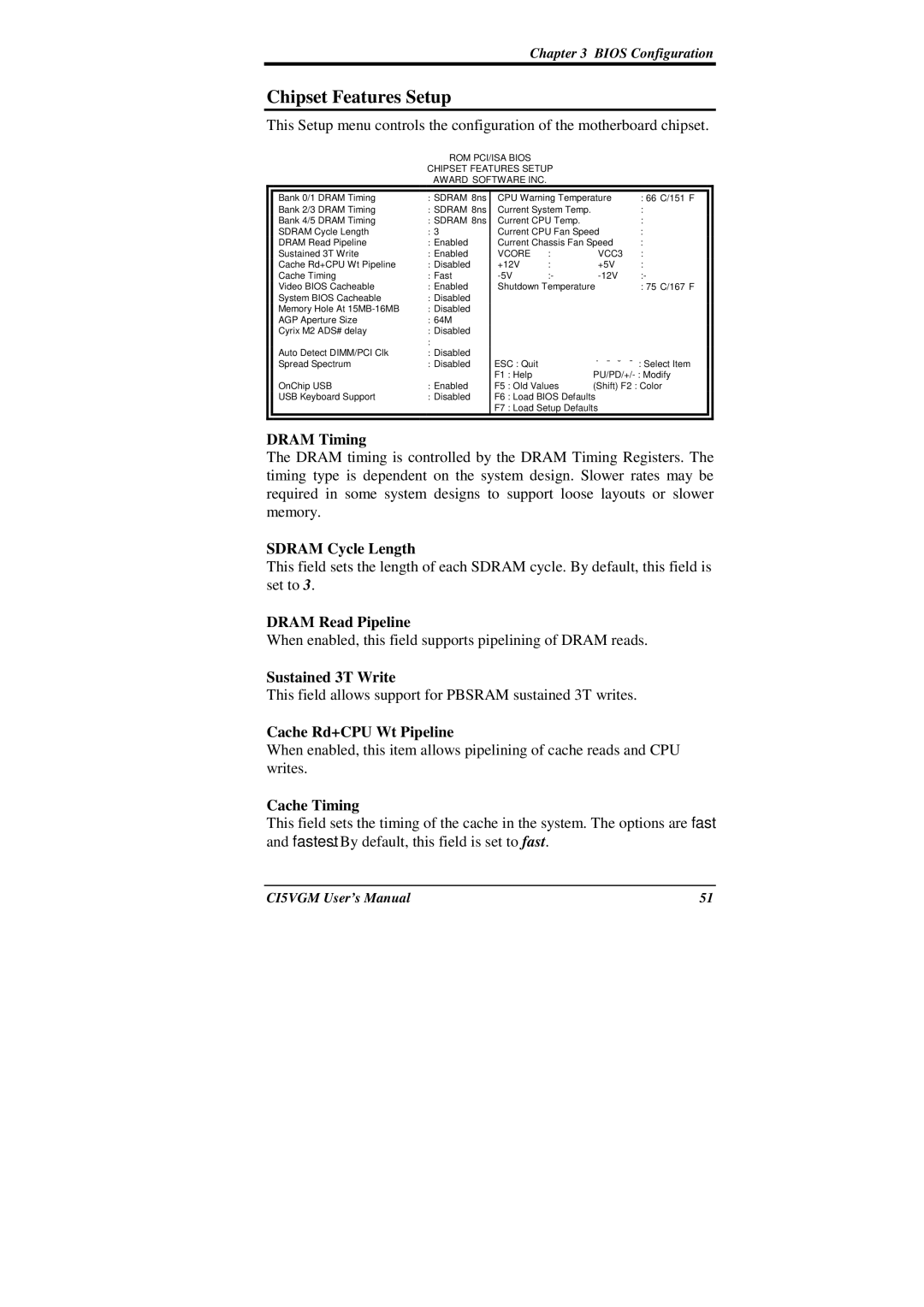

This Setup menu controls the configuration of the motherboard chipset.

ROM PCI/ISA BIOS

CHIPSET FEATURES SETUP

AWARD SOFTWARE INC.

|

|

|

|

|

|

|

|

|

| Bank 0/1 DRAM Timing | : | SDRAM 8ns | CPU Warning Temperature | : 66° C/151° F |

| ||

| Bank 2/3 DRAM Timing | : | SDRAM 8ns | Current System Temp. |

| : |

| |

| Bank 4/5 DRAM Timing | : | SDRAM 8ns | Current CPU Temp. |

| : |

| |

| SDRAM Cycle Length | : | 3 | Current CPU Fan Speed | : |

| ||

| DRAM Read Pipeline | : | Enabled | Current Chassis Fan Speed | : |

| ||

| Sustained 3T Write | : | Enabled | VCORE | : | VCC3 | : |

|

| Cache Rd+CPU Wt Pipeline | : | Disabled | +12V | : | +5V | : |

|

| Cache Timing | : | Fast | :- | :- |

| ||

| Video BIOS Cacheable | : | Enabled | Shutdown Temperature | : 75° C/167° F |

| ||

| System BIOS Cacheable | : | Disabled |

|

|

|

|

|

| Memory Hole At | : | Disabled |

|

|

|

|

|

| AGP Aperture Size | : | 64M |

|

|

|

|

|

| Cyrix M2 ADS# delay | : Disabled |

|

|

|

|

| |

|

| : |

|

|

|

|

|

|

| Auto Detect DIMM/PCI Clk | : Disabled |

|

|

|

|

| |

| Spread Spectrum | : Disabled | ESC : Quit |

| Ç È Æ Å : Select Item |

| ||

|

|

|

| F1 : Help |

|

| ||

| OnChip USB | : Enabled | F5 : Old Values | (Shift) F2 : Color |

| |||

| USB Keyboard Support | : Disabled | F6 : Load BIOS Defaults |

|

| |||

|

|

|

| F7 : Load Setup Defaults |

|

| ||

|

|

|

|

|

|

|

|

|

DRAM Timing

The DRAM timing is controlled by the DRAM Timing Registers. The timing type is dependent on the system design. Slower rates may be required in some system designs to support loose layouts or slower memory.

SDRAM Cycle Length

This field sets the length of each SDRAM cycle. By default, this field is set to 3.

DRAM Read Pipeline

When enabled, this field supports pipelining of DRAM reads.

Sustained 3T Write

This field allows support for PBSRAM sustained 3T writes.

Cache Rd+CPU Wt Pipeline

When enabled, this item allows pipelining of cache reads and CPU writes.

Cache Timing

This field sets the timing of the cache in the system. The options are fast and fastest. By default, this field is set to fast.

CI5VGM User’s Manual | 51 |