8086

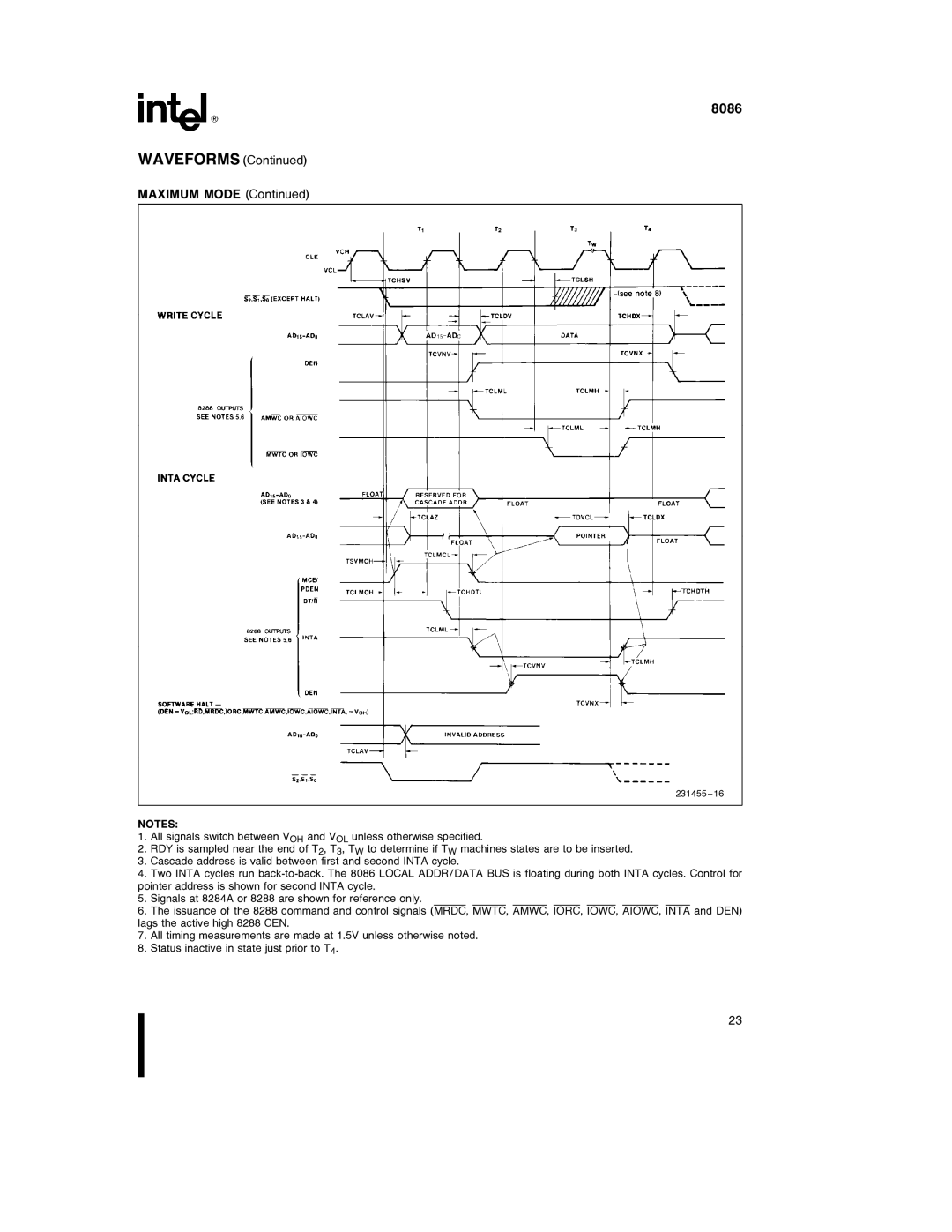

WAVEFORMS (Continued)

MAXIMUM MODE (Continued)

231455 – 16

NOTES:

1.All signals switch between VOH and VOL unless otherwise specified.

2.RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

3.Cascade address is valid between first and second INTA cycle.

4.Two INTA cycles run

5.Signals at 8284A or 8288 are shown for reference only.

6.The issuance of the 8288 command and control signals (MRDC, MWTC, AMWC, IORC, IOWC, AIOWC, INTA and DEN) lags the active high 8288 CEN.

7.All timing measurements are made at 1.5V unless otherwise noted.

8.Status inactive in state just prior to T4.

23