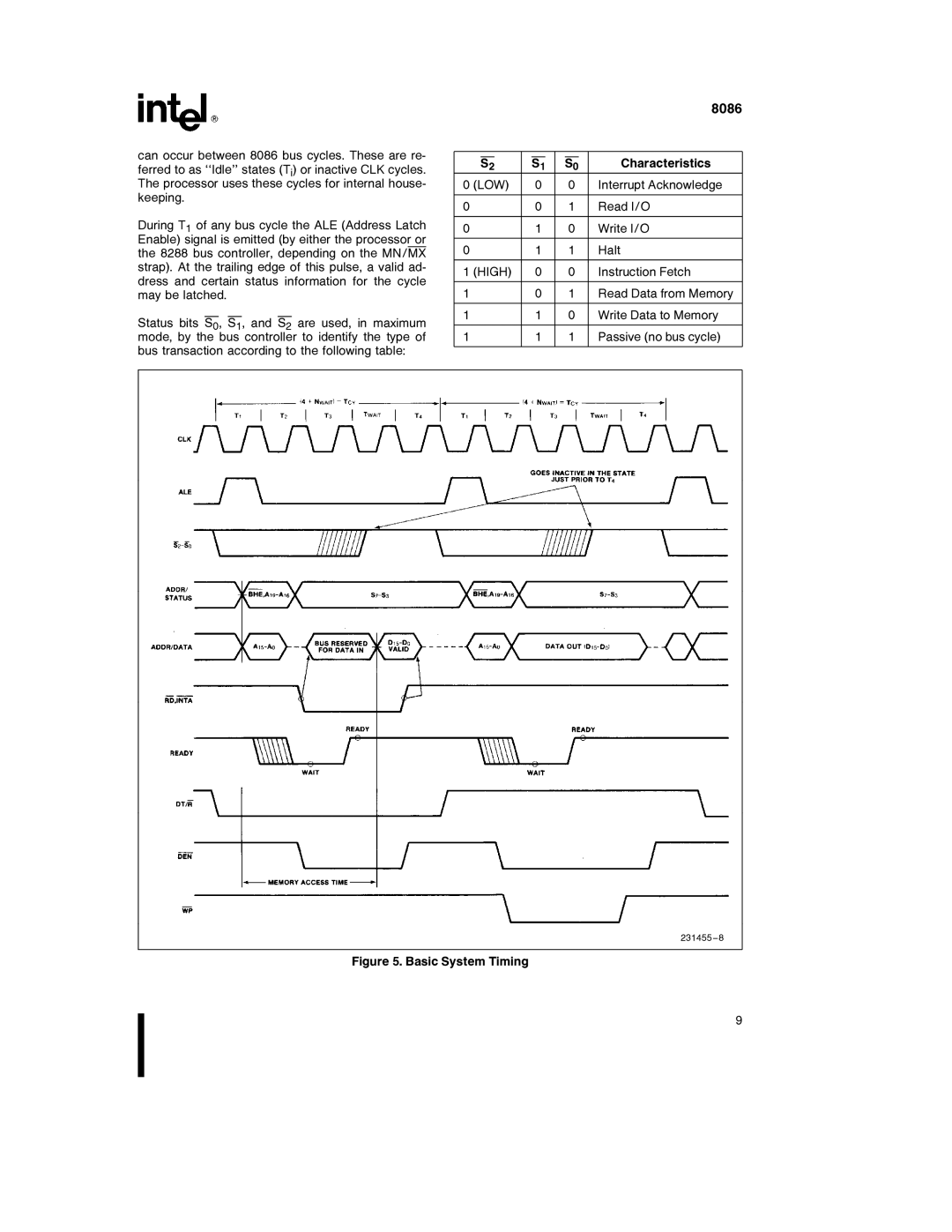

can occur between 8086 bus cycles. These are re- ferred to as ‘‘Idle’’ states (Ti) or inactive CLK cycles. The processor uses these cycles for internal house- keeping.

During T1 of any bus cycle the ALE (Address Latch Enable) signal is emitted (by either the processor or the 8288 bus controller, depending on the MN/MX strap). At the trailing edge of this pulse, a valid ad- dress and certain status information for the cycle may be latched.

Status bits S0, S1, and S2 are used, in maximum mode, by the bus controller to identify the type of bus transaction according to the following table:

|

|

|

|

|

|

|

|

|

| 8086 |

|

|

|

|

|

|

|

|

|

|

|

| S2 | S1 | S0 | Characteristics | ||||||

0 | (LOW) | 0 |

| 0 |

| Interrupt Acknowledge | ||||

|

|

|

|

|

|

|

|

| ||

0 |

|

|

| 0 |

| 1 |

| Read I/O | ||

|

|

|

|

|

|

|

|

| ||

0 |

|

|

| 1 |

| 0 |

| Write I/O | ||

|

|

|

|

|

|

|

|

| ||

0 |

|

|

| 1 |

| 1 |

| Halt | ||

|

|

|

|

|

|

| ||||

1 | (HIGH) | 0 |

| 0 |

| Instruction Fetch | ||||

|

|

|

|

|

|

|

|

| ||

1 |

|

|

| 0 |

| 1 |

| Read Data from Memory | ||

|

|

|

|

|

|

|

|

| ||

1 |

|

|

| 1 |

| 0 |

| Write Data to Memory | ||

|

|

|

|

|

|

|

|

| ||

1 |

|

|

| 1 |

| 1 |

| Passive (no bus cycle) | ||

|

|

|

|

|

|

|

|

|

|

|

231455 – 8

Figure 5. Basic System Timing

9